AUTOMATION TECHNOLOGY (FOUO 13/80)

23 JULY 1980

1 OF 2

JPRS L/9206 23 July 1980

# **USSR** Report

CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY

(FOUO 13/80)

FOREIGN BROADCAST INFORMATION SERVICE

#### NOTE

JPRS publications contain information primarily from foreign newspapers, periodicals and books, but also from news agency transmissions and broadcasts. Materials from foreign-language sources are translated; those from English-language sources are transcribed or reprinted, with the original phrasing and other characteristics retained.

Headlines, editorial reports, and material enclosed in brackets [] are supplied by JPRS. Processing indicators such as [Text] or [Excerpt] in the first line of each item, or following the last line of a brief, indicate how the original information was processed. Where no processing indicator is given, the information was summarized or extracted.

Unfamiliar names rendered phonetically or transliterated are enclosed in parentheses. Words or names preceded by a question mark and enclosed in parentheses were not clear in the original but have been supplied as appropriate in context. Other unattributed parenthetical notes within the body of an item originate with the source. Times within items are as given by source.

The contents of this publication in no way represent the policies, views or attitudes of the U.S. Government.

For further information on report content call (703) 351-2938 (economic); 3468 (political, sociological, military); 2726 (life sciences); 2725 (physical sciences).

COPYRIGHT LAWS AND REGULATIONS GOVERNING OWNERSHIP OF MATERIALS REPRODUCED HEREIN REQUIRE THAT DISSEMINATION OF THIS PUBLICATION BE RESTRICTED FOR OFFICIAL USE ONLY.

HARDWARE

# FOR OFFICIAL USE ONLY

JPRS L/9206

23 July 1980

# USSR REPORT

# CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY

(FOUO 13/80)

# CONTENTS

| Т        | The M5100 Computer Complex. Operating Principles                                                  | 1  |

|----------|---------------------------------------------------------------------------------------------------|----|

| G        | General Characteristics of the M5100 Computer Complex                                             | -  |

| P        | Principles of Organization of Multimachine Complexes                                              | 33 |

| I        | The M5100 Computer Complex Instruction Format                                                     | 34 |

| M        | dicroelectronics and Semiconducting Instruments                                                   | 3  |

| APPLICAT | rions                                                                                             |    |

| F        | Holography and Optical Data Processing in Geology and Geophysics                                  | 7  |

| נ        | The Problem of Processing Large Masses of Geological and Geophysical Data and Ways to Solve It    | 8  |

| (        | Optico-Electronic System of Image Analysis Based on an Optical Correlator and Electronic Computer | 9  |

| A        | Analysis and Interpretation of Instability in a Liquid-Crystal  Matrix "With a Memory"            | 9  |

| PUBLICAT | TIONS                                                                                             |    |

| (        | Computer Technology of Socialist Countries                                                        | 9  |

| (        | Computer Technology of Socialist Countries                                                        | 9  |

| τ        | Use of Electronic Computer Technology in Socialist Countries                                      | 9  |

| I        | Dialogue Sector Information System Based on the YeS-1040                                          | 10 |

- a - [III - USSR - 21C S&T FOUO]

| Microprocessor Data Processing System for Formation of Rolling Stock at Shunting Stations                                                                                | 106 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| System of Programs and Hardware for Monitoring Digital Circuits                                                                                                          | 109 |

| Automated Control System Based on the YeS-1032 Computer                                                                                                                  | 111 |

| System of Calendar Planning of Mini-Type Production                                                                                                                      | 114 |

| Data Base Control System DBS/R for Subsystems of the Complex "Work Force"                                                                                                | 116 |

| Automation of Production of Programs of the International System of Small Computers Using Large and Small Computers                                                      | 117 |

| Structure of Programming Software of Control Computer Complexes of the International System of Small Computers With Main Circuit Structure                               | 121 |

| Applied Program Packages for Identification, Simulation,<br>Analysis and Synthesis of Automated Control Systems                                                          | 126 |

| APL Programming SystemEffective Tool of Analysis and Synthesis of Digital Systems                                                                                        | 128 |

| Realization of Applied Program Packages for Technical and Economic Planning                                                                                              | 130 |

| On One Approach to Realization of Principles of Closed Systems for Development of Data Base Management Systems (SUBD) of Integrated Data Processing System (SIOD) Family | 131 |

| First Compatible Tests of Hardware and Programming Devices of<br>the International System of Small Computers (SM EVM)                                                    | 132 |

| Verification of the Operating Efficiency of the YeS-1021 Computer                                                                                                        | 138 |

| Systems Programming Software for Industrial Tests of Peripheral Devices. Devices for Processing Statistical Information                                                  | 149 |

| Problems of Raising Qualifications of Personnel in Base Programming Software                                                                                             | 150 |

- b -

FOR OFFICIAL USE ONLY

3

# FOR OFFICIAL USE ONLY

| Problems of Raising Qualifications of Experts in ASU Programming Software Based on Applied Program Packages | 153 |

|-------------------------------------------------------------------------------------------------------------|-----|

| Information on New SM EVM Computer Hardware                                                                 | 157 |

| Polish Magnetic Tape Memories                                                                               | 164 |

| Programming Systems for the YeS-1030 Computer                                                               | 168 |

| Programs for Realizing Mathematical Methods in the Operating Systems OS YES                                 | 169 |

| Annotations from "Computer Technology of Socialist Countries".                                              | 179 |

# HARDWARE

#### THE M5100 COMPUTER COMPLEX. OPERATING PRINCIPLES

Moscow VYCHISLITEL'NYY KOMPLEKS M5100. PRINTSIPY RABOTY (The M5100 Computer Complex. Operating Principles) in Russian 1979 signed to press 17 May 1979 pp 2, 3-4

[Annotation, table of contents and foreword from book by Bronislovas Bronislavovich Belyauskas, Regina Ionovna Valatkayte and Antanas Mikolovich Nemeykshis, Statistika, 17,500 copies, 144 pages]

Ē

# [Text] Annotation

A new computer complex, the M5100, its structure and main principles of organization and also the technical means of reorganization of two-machine complexes are examined in the book.

The book is intended for users of the complex and can be useful to persons studying questions about the architecture and structure of electronic computers.

# Contents

|          |                                                                                                                                         | Page        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Foreword | 1                                                                                                                                       | 3           |

| 1.1.     | 1. General Characteristics of the M5100 Computer Complex<br>Structure of the Complex<br>Basic Composition and Alternatives of Execution | 5<br>5<br>9 |

| 1.3.     | Technical Characteristics of the Equipment Data Preparation System                                                                      | 12<br>16    |

| 1.5.     | Technical Servicing of the Complex<br>Brief Characterization of the Software                                                            | 19<br>21    |

| ·        | Prospects of Development of the Complex                                                                                                 | 26          |

| -        | 2. Distinctive Features of the Architecture and Functioning of the Complex                                                              | 29          |

| 2.1.     | Similarity and Differences of Various Models of the Model M5000 Machine                                                                 | 29          |

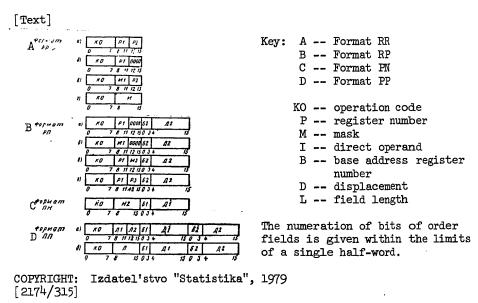

| 2.2.     | New M5100 Computer Complex Orders                                                                                                       | 32          |

1

|                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <ol> <li>Register of State of the Program</li> <li>Storage Protection</li> <li>The Interruption System</li> <li>Apparatus Control</li> <li>The Operating Principle of the Timer and Clocks</li> <li>The Operator's Panel</li> <li>The Initial Load of Disk Operating Systems and Test Programs</li> </ol>                                                                                                                      | 37<br>39<br>42<br>45<br>51<br>52<br>54 |

| Chapter 3. The Central Processor 3.1. The Structure of the Central Processor 3.2. The Processor Working Regime 3.3. The Engineer's Panel 3.4. Procedures of Inspection and Change of the Contents of the Immediate-Access Memory                                                                                                                                                                                               | 59<br>59<br>63<br>64<br>68             |

| Chapter 4. Organization of Input-Output 4.1. Apparatus and Program Means of Input-Output 4.2. Fields of Control of Input-Output Operations 4.3. The Word of Channel State 4.4. Input-Output Orders 4.5. Procedure for Interruption of an Input-Output Class 4.6. Switching On and Identification of Devices 4.7. Functioning of the Input-Output Interface 4.8. Structure and Operating Principle of an Input-Output Processor | 70<br>76<br>79<br>82<br>85<br>86<br>89 |

| Chapter 5. Operations of Input-Output Devices 5.1. Operation of the R212 Control Panel                                                                                                                                                                                                                                                                                                                                         | 100<br>100                             |

| 5.2. The Operations of Data Input From Punched Tape and Output to Punched Tape                                                                                                                                                                                                                                                                                                                                                 | 103                                    |

| <ul><li>5.3. The Operations of Data Input From Punched Cards and Output to Punched Cards</li><li>5.4. The Operation of Printing</li><li>5.5. Organization of the Performance of Magnetic Disk</li></ul>                                                                                                                                                                                                                        | 107<br>110                             |

| Store Operations 5.6. Organization of the Performance of Magnetic Tape Store Operations                                                                                                                                                                                                                                                                                                                                        | 112<br>125                             |

| Chapter 6. Organization of Multimachine Complexes 6.1. Principles of Organization of Multimachine Complexes 6.2. Functioning of M5100-M5000 Channel Adapters                                                                                                                                                                                                                                                                   | 130<br>130<br>132                      |

| Appendix 1. Making Up Complete Sets of Equipment in Various Executions of the M5100 Computer Complex Appendix 2. M5100 Computer Complex Order Formats Appendix 3. M5100 Computer Complex Order List Appendix b. Time Required for the Frequency of Orders                                                                                                                                                                      | 137<br>137<br>138                      |

2

#### Foreword

Ī

Computers of the M5000 type, specialized for the conducting of mass economic calculations, have found wide application in the national economy of the country. Those computers are small electronic computers, well-suited for the processing of large masses of alphanumeric data and successfully used in computing and data processing centers and stations of the USSR Central Statistical Administration system, and also in the computer centers of small industrial and non-industrial enterprises. For the M5000 and M5010 computers both general software representing the basis of successful and effective use but also practical software in the spheres of statistics, trade, agriculture, industrial and transport enterprises, etc.

The computer complex M5100 is a new model in the family of the model M5000 computers. This computer represents a further development of the hardware and architecture constituting the base of the preceding models of the M5000 machines. Together with that, in the M5100 computer complex a number of new technological solutions have been introduced that assure some additional possibilities and greater capacity than preceding models. The differences in those solutions do not exclude, however, continuity in the family of computers of that type, that is, the new model is compatible with preceding models with respect to software. All the practical software developed for the M5000 and M5010 complexes can be used in solving problems with the use of apparatus of the M5100 computer complex. The software compatibility of the M5000 and M5010 models with the M5100 computer complex facilitates its introduction, in particular, in organizations that already have experience in the use of computers of the M5000 type.

The high capacity of the M5100 computer complex is its main difference from preceding models. The increase in capacity was achieved thanks to increase of the internal speed of the processor, rearrangement of input-output control, increase of the volume of the working storage and the external immediate-access storage, organization of the multi-program regime, etc. All this contributes to expansion of the range of problems solved with computers of type M5000.

The functional possibilities of the complex have also been expanded in another direction. The hardware and software of the complex allow the possibility of organizing two-machine complexes based on the M5100 computer complex and the M5010. In addition, interaction with other computers or terminals through outlets on the communications line is assured.

The architecture of the M5100 computer complex takes into consideration the clearly noted tendency toward replacement of punched data carriers by magnetic carriers. Actually, punched cards and tapes have great shortcomings in the quality of the means of storage of primary or intermediate data. More promising in that respect are magnetic carriers, that is, magnetic tapes and disks. At the present time there already exists the R810 date preparation system (see section 1.4), intended for the registration

of data from a primary document directly on a magnetic disk. One should expect in the future the appearance of devices for the preparation of data on magnetic carriers of other types, and also the possibilities of preparing data by means of the computers themselves. These trends have been reflected in the organization of the connection of peripherals to the M5100 computer complex in general and, in particular, in the expansion of types and the number of magnetic disk and tape stores. This assures convenience of data storage and immediate access to those data.

The authors examine the logical structure and operating principles of the complex as a whole and its separate devices, and also present some comparative data. In the presentation of the material the authors started from the fact that the readers are already acquainted with the M5000 computer from the book "Perforatsionnyy vychislitel'nyy kompleks M5000" (The M5000 Perforation Computer Complex), Moscow, Statistika, 1970). And so attention is given here to aspects of the architecture of the M5100 complex and the devices that are new and distinguish that comples from preceding models. The software is an independent subject and is examined only to the extent necessary to explain the main material of the book.

COFYRIGHT: Izdatel'stvo "Statistika", 1979 [2174/315]

2174 CSO: 1863

#### GENERAL CHARACTERISTICS OF THE M5100 COMPUTER COMPLEX

Moscow VYCHISLITEL'NYY KOMPLEKS M5100. PRINTSIP RABOTY (The M5100 Computer Complex. Operating Principles) in Russian 1979 signed to press 17 May 1979 pp 5-28

[Chapter 1 from book by Bronislovas Bronislavovich Belyauskas, Regina Ionovna Valatkayte and Antanas Mikolovich Nemeykshis, Statistika, 17,500 copies, 144 pages]

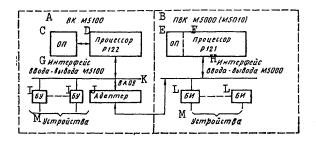

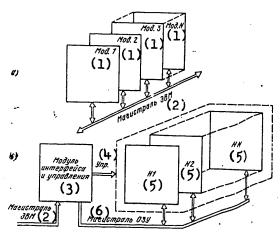

# [Text] 1.1. Structure of the Complex

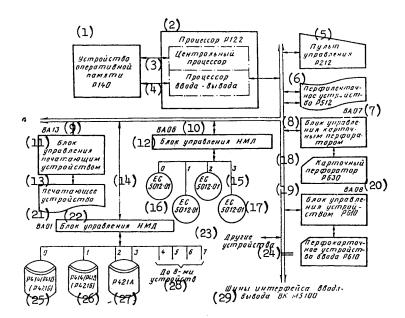

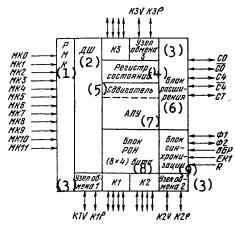

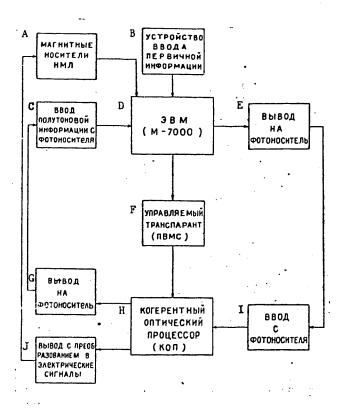

The M5100 computer complex is a set of logically completed devices with various functional purposes that allow their being combined into a system that constitutes its own specific variant of execution of the complex, that is, a specific electronic computer. A certain portion of the devices of the complex is necessary in each execution, and some devices of the complex can be connected selectively to create necessary configuations in accordance with the group of problems to be solved and the needs of the user. The block diagram (Fig 1.1) illustrates the composition of the complex and the logical principles of its construction and expansion.

The immediate-access storage is realized in the form of an independent R140 device and is intended for the storage of programs and data directly participating in computations. The immediate-access storage is loaded with data from external carriers through an input-output device.

The R122 processor is intended for the performance of all operations on data in accordance with the instructions list. In spite of the fact that the R122 processor is made as a separate structural unit of the complex, in considering the operating principles it is convenient to consider that it includes two independent functional parts: the central processor and the input-output processor. The functions of the central processor include the readout of program instructions from the immediate-access storage, the interpretation of instructions and the performance of operations on data, including the disposition of a result, the modification of addresses and other actions. However, if the program instruction requires any sort of actions connected with the functioning of the equipment and external in relation to the R122 processor and the immediate-access storage, then the

5

central processor actuates the input-output processor, communicating the necessary control data to it. The functions of the input-output processor include organization of data exchange between the immediate-access storage and the external carriers, including all actions in the control of the equipment. In executing its functions the input-output processor acts independently of the central processor up to completion of exchange operations.

The input-output processor is equipped with standardized outputs in the direction of the peripheral part of the complex -- toward the input-output devices, the external stores and other equipment. By standardized outputs should be understood a system of busses and signals determined by the M5100 computer complex input-output interface. The general principle of connection of the devices determined the following path of data exchange between the input-output processor and the devices: the interface lines, the equipment control unit or group of devices and the device. In that case the outputs of all control units in the direction of the input-output processor are determined by a standard set of signals and procedures in accordance with the input-output interface of the M5100 computer complex, and the outputs in the direction of the devices are different and are determined by the specifics of the devices themselves. The main purpose of the control units is coordination of the logical and electrical parameters of the devices with the parameters of the central part of the complex. The volume of the apparatus of the control units and their specific functions are determined by the type of connected devices.

The input-output devices have an R212 control panel, an R512 input-output tape perforator, an R630 card puncher, an R610 punched-card input and printers.

The R212 control panel is the main means of control of the work of the complex. The panel includes a control unit, a printer and the operator's panel of the system.

The printer is the means by which the operator has a dialog with the machine. In the process of executing programs it prints information on the course of the work of the complex, gives instructions to the operator on the performance of any previously envisaged actions, or informs him of the need to make a decision when there are alternative possibilities of continuing the work. The operator's instructions are introduced from the keyboard of the control panel printer and are simultaneously printed, and that assures documentation of the entire operator-machine dialog.

The operator's punel of the system contains necessary luminous signals that indicate to the operator normal or emergency situations in the functioning of the system. By means of that panel the regimes for execution of tasks of the complex are started, stopped or changed.

The R512 tape unit is intended for the input and output of data, the external carrier of which is punched paper tape. The device consists of

6

Fig 1.1. Structure of the M5100 computer complex.

- 1 -- R140 immediate-access storage 2 -- R122 processor

- 3 -- Central processor

- 4 -- Input-output processor

- 5 -- R212 control panel 6 -- R512 tape unit

- 6 -- R512 tape w 7 -- VAO7

- 8 -- Card puncher control unit

- 9 -- VA13

- 11 -- Printer control unit

- 12 -- Magnetic tape storage control

- 13 -- Printer

- 14 to 17 -- YeS-5012-01 computers

- 18 -- R630 card puncher

- 19 -- R610 control unit

- 20 -- VA08

- 21 -- VAO1

- 22 -- Magnetic disk store control

- 23 -- Device address

- 24 -- R610 card puncher

- 25 and 26 -- R414 (R412) (R421B)

- 27 -- R421A

- 28 -- To 8th device

- 29 -- Interface buses of M5100 computer complex interface

a control unit, a device for readout of data from punched tape (FS-1501) and a FL-150 perforator.

The R630 card punch serves for the output of data, the external carrier of which is a standard 80-column punched card. The R630 punch is connected to the machine through a VA07 control unit. Besides its main function of signal matching the control unit recodes data from the internal code of the M5100 computer complex into the punched card code. In that unit provision

7

is made for a memory for the brief storage of data in the volume of two punched cards in order to free the input-output processor from tracking the position of the perforator mechanism and to assure the monitoring of perforation.

The R610 input punch is used for the input of data, the carrier of which is a standard 80-column punched card. The device is connected through a VAO8 control unit which accomplished the logical and electrical matching of signals, and also transformation of the data code from the punched card code into the internal code of the M5100 computer complex.

The printer is used in the complex for the output of informational reports of the operating system and the output of the results of calculations in the form of printed documents--forms, lists, tables, etc. The device is connected through a VAl3control unit. A wide-format printing device of the ATSPU-128-3M or DV-313 type can be connected to that unit.

In the M5100 complex use is made of two external stores: magnetic tape stores and magnetic disk stores. Each type, with its control units, forms an external memory of the complex on magnetic tapes and magnetic disks.

The external magnetic tape store is intended mainly for the long-term storage of large masses of data in cases where operative access to data is not required, for example, during the storage of copies, archive data, etc. Magnetic tape stores can be used for the brief storage of data during transcriptions from some carriers to others and, finally, magnetic tape stores can be used as systems equipment intended for control of the process of fulfilment of tasks. Used in the M5100 computer complex are YeS-5012-01 magnetic tape stores, which are connected to the complex through a VAO6 general control unit in a quantity not exceeding 4.

The external magnetic disk store occupies an intermediate position between the immediate-access memory and such external carriers as magnetic tape stores, in view of their relatively high speed, the possibility of direct access to data and fairly great capacity. On magnetic disk stores is the main load in the solution of most problems with the application of the complex. This applies to such operations in putting masses of data in order as sorting, the formation of new masses through merging, etc. It should be emphasized that the performance of such procedures with the use of magnetic disks gives the main effect from the application of the complex in the area of the processing of economic and statistical data.

In the complex, magnetic disk stores are used in three main directions:

--for the storage of programs of the operational system;

--for the operational storage of intermediate data during the execution of tasks:

-- for the long-term storage of data requiring immediate access.

Since a magnetic disk store is the place of storage of programs of the operational system, it continuously participates in the control of work

of the complex. The portion of the total volume of magnetic disk storage intended for the storage of programs of the operational system must be constantly preserved and renewed for the purpose of assuring the normal functioning of the complex. The remaining portion of the magnetic disk storage can be used arbitrarily with respect to the performed work and needs of the user. For example, the most frequently run programs of the user can be stored in the magnetic disk store.

Devices of types R412, R414, R421A and R421B can be used as magnetic disk stores in the complex; they are connected through the general control disk by VAOl disk stores, and their total number does not exceed 8.

All the devices have a modular structure, both in a functional respect and in respect to design execution. A device or group of devices, together with the entire control unit, can be removed from the makeup of the complex without any sort of changes in the remaining part of it. Any new device can be connected to the complex if it is equipped with a control unit with an output corresponding to the interface of the M5100 computer complex.

From the point of view of the dynamics the work of the M5100 computer complex is based on the use of the following principles:

--independence of the work of individual devices from one another;

--maximum coincidence in the time of performance of internal operations and operations of exchange with input-output devices.

The independence of the work of individual devices should be understood as the possibility of independent functioning of all outputs from the control units to the input-output processor and in the reverse direction. The action of devices connected to a single control unit should generally have limitations. Thus, operations of the exchange of data simultaneously by two magnetic disk store or two magnetic tape store devices are not permitted. At the same time, in a group of devices of the same kind it is possible to combine the performance of one exchange operation with the performance of one or more control operations, for example, readout of a tape in one device and rewinding of the tape in another magnetic tape device. If the control unit has several outputs in the direction of the interface, the work of devices connected to it can be combined. For example, the control unit in the R512 device permits readout of data from punched tape and simultaneous perforation.

The independence of the control of devices and the high throughput capacity of an input-output processor assure the possibility of combining in time the operations of exchange of all groups of devices with consideration of the above enumerated limitations. In general the sequence of the work of devices and the degree of coincidence are determined by the programs. The operations of peripheral units are controlled by the input-output processor in accordance with the established order of priority of servicing of the devices. Thus magnetic disk stores, as the most rapid peripheral unit, have

9

the highest priority in the combination of the work of peripherals. However, devices of the same type in a group have identical priority and the device is serviced toward which the program refers.

Envisaged to a considerable degree in the architecture of the complex is independent action of the central processor and the input-output processor during the time of data exchange with the immediate-access storage and the input-output devices. It was pointed out earlier that from the moment an instruction is obtained until the operation of exchange is completed the input-output processor acts independently of the central processor, refers independently to the immediate-access storage for the disposition or reception of data relating to external carriers. The central processor is equipped with its own means of reference to the immediate-access store. The R140 immediate-access store device services two processors in proportion to the arrival of requests for servicing. When requests arrive simultaneously the priority is presented to the input-output processor, which assures the rapid disposition of data from external carriers. It is natural that in such an organization both processors must have minimum means of buffering data for the necessary waiting time. In that case the state of the devices is monitored by the software of the complex and instructions are issued to peripherals for the purpose of organizing a continuous processing of the flow of data.

# 1.2. Basic Composition and Alternatives of Execution

Fig 1.1 presents the functional devices and units entering the basic composition of the complex: the immediate-access store, processor, control panel, punched tape and card input-output devices, printers, magnetic disk stores and magnetic tape stores. To power those devices, the basic composition also includes an ROOl unit (not shown on the diagram). Installed in that device is all the apparatus for manual switching of network voltage on and off, both for the complex as a whole and for its separate devices, apparatus for the automatic switching off of the power network in emergency situations and network filters for its protection against noises arising during operation of devices of the complex.

Still another component of the basic composition of the complex is software delivered to the user in the form of a set of carriers with recordings and corresponding operational documentation. The composition of the software is examined in section 1.6.

A specific electronic computer, constructed on the basis of devices of the M5100 computer complex, does not obligatorily contain all components of the basic composition of the complex. Obligatory components in any form of a complex are the R140 immediate-access storage, an R122 processor, an R212 control panel, an R001 power unit and software. Other devices of the basic composition can be switched on in different combination; this makes it possible to form electronic computers with different capacity in accordance with the needs of the user.

10

The manufacturers have proposed issuing the M5100 computer complex of the basic composition in five alternative types (Appendix 1) differing mainly in the type of magnetic disk and tape stores included.

The inclusion in the complex of special-purpose devices, that is, adapters, apparatus for output to communication lines and video terminals (see 1.7) must be agreed upon with the manufacturers of the complex.

The formation of alternative units (specific electronic computers) is based on the modular principle of construction of separate component parts of the complex in both functional and design respects. The combination of devices of the complex into a single electronic computer is accomplished on the basis of a rigid previous plan for arrangement of the apparatus. A specific set of devices together with a specific set of installation complexes that include connective cables, standard couplings intended for the electrical connection to the standard outputs of an input-output processor, and other necessary parts, also constitute a specific variant of execution of the complex.

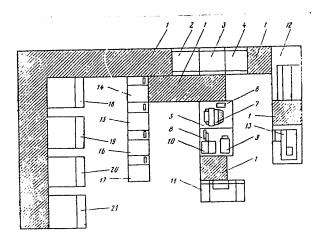

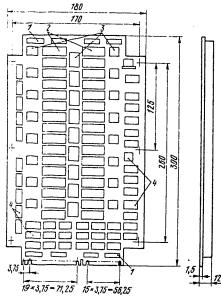

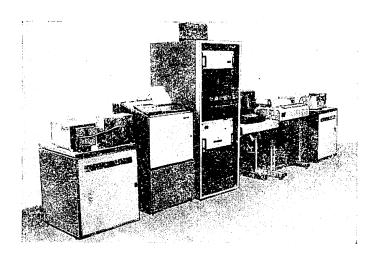

All the apparatus (Fig 1.2) is installed around a rigid metal loop 1--of boxes intended for the laying of connecting cables between equipment with the requirements of reliability and noise resistance of the connections taken into consideration. The obligatory parts of any form of the complex are arranged in columns designated on Fig 1.2 by the positions 2, 3 and 4. In column 2 is the ROOl power equipment, in column 3 the R140 immediate-access store, and in column 4 the R122 processor. An obligatory component part also is the R212 control panel (5) with the operator's panel for the system 6 and the printer 7.

Fig 1.2. Arrangement of apparatus of the M5100 computer complex

11

# FOR OFFICIAL USE ONLY

The R512 input-output tape unit (8) is made in the form of a single structural unit that includes an FS-1501 device for readout from punched tape, a PL-150 tape perforator (10) and their control unit. An ATSPU-128-3M or DB-313 printer is designated by position 11. The control unit of the VA13 printer is set in the rack of the R512 console. That unit is an interchangeable independent structural and functional unit and when the type of printer is changed can be replaced by another unit that matches the device used.

The R630 card puncher (12) and the R610 punched card input (13) are installed in a single design type with its own VAO7 and VAO8 control units respectively.

The magnetic disk stores (14-17) can be of any types in a combination provided for by the alternative types of system. Their control unit VAOl is in rack 3 instead of the immediate-access store and represents an independent interchangeable structural unit.

The magnetic tape stores (18-21) are installed in a quantity of not more than 8. The VAO6 tape control unit is put in rack 3.

The physical outputs of the input-output processor, corresponding to the M5100 computer complex input-output interface, are arranged in rack 4. The outputs are occupied by standardized TS coupling elements if the device is connected through them. From the coupling elements to the control units of the devices run connecting cables through which radial connections of the physical outputs of the input-output processor and the devices are accomplished.

If a device of any type is absent in a specific electronic computer, then the corresponding coupling element also will be absent, as will the control unit and the set of connecting cables, and the loop 1 will be reduced to dimensions corresponding to the specific execution.

The connection to the complex of any new device above the basic composition requires the presence of outputs corresponding to the M5100 computer complex input-output interface and the making of the control unit with observance of the construction standards of M5100 computer complex apparatus.

1.3. Technical Characteristics of the Equipment

Before examining the technical characteristics of the equipment, we will dwell on some indicators characterizing the M5100 computer complex as a computer on the whole.

1. The M5100 computer complex is compatible as regards programming with M5000 models of the machines produced earlier as regards programs of the user and information carriers.

Compatibility on the level of user programs means the possibility of running on the M5100 computer complex programs developed for the M5000 and M5010 computer complexes. However, in view of the fact that new orders and programs created with their use have been included in the order set of the M5100 computer complex, they will be run only on the M5100 computer complex.

Used in the M5100 complex as information carriers are punched cards and tapes and magnetic disks and tapes, that is, the same information carriers as in preceding models of machines of the M5000 type. Compatibility on the carrier level can be regarded as physical compatibility and compatibility with respect to information coding. The direct use of carriers of preceding models of the M5000 type of machine allows magnetic disks and tapes on which information is stored in the internal code of the machine. The data format on the magnetic tape corresponds to ISO recommendations Nos 1862 and 1863.

The data on punched cards are presented in the code of All-Union State Standard 19769-74, and the data on punched tape in the code of either All-Union State Standard 13052-74 or of MTK-2M. The presentation of data on punched cards and tapes in other codes also is allowed, but in data input and output in that case programmed precoding by means of programs of the operational system is required.

2. The M5100 computer complex permits connection to 128 input-output devices.

The devices are connected through 16 physical outputs of the input-output processor. Each physical output allows the connection of up to 8 devices of the same kind, controlled by a single control unit.

3. Reference to M5100 computer complex equipment occurs by means of physical addresses established during the development of the control units. Priority of servicing of devices by the input-output processor when they are simultaneously put in operation is determined by the place of connection of those equipment to the standard outputs of the input-output processor (the output number).

For equipment of the basic composition of the M5100 computer complex the following physical addresses have been established (the addresses are presented in sexadecimal representation):

| magnetic disk stores                  | 00, 01, 02, 03, 04, 05, 06, 0 | )7 |

|---------------------------------------|-------------------------------|----|

| magnetic tape stores                  | 08, 09, 0A, OB                |    |

| printers                              | 10, 18                        |    |

| card punch                            | 20                            |    |

| R512 device (input from punched tape) | 28                            |    |

| card punch of R610 input              | 30                            |    |

| R512 device (output on punched tape)  | 38                            |    |

| control panel                         | 40                            |    |

13

#### FOR OFFICIAL USE ONLY

The R122 processor performs operations on binary, decimal and symbolic data arranged in the immediate-access storage and controls data exchange between the immediate-access and external storage in accordance with the program orders.

Technical Characteristics

Capacity

Number system Representation of alphanumeric characters Decimal data length

Alphanumeric data length Form of number representation Order length Number of addresses in an order Number of basic orders Processor cycle Average time required for completion of operations on two 4-digit decimal numbers: comparison addition multiplication division Possibility of multiprogram work

Storage protection Interruption system Input-output regime Input-output rate

at least 30,000 orders/s in the solution of tasks in economic planning binary-decimal

8 informational bits, 1 control variable, from 1st to 31st decimal place variable, from 1 to 256 characters with fixed point variable, 2, 4 or 6 bites 0, 1 or 2 61 0.625 microsecond

25 microseconds

30 11 150 250

execution of up to three working programs

program-circuit

multiplex

up to 500 Kbites/s

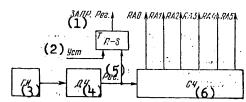

The immediate-access storage is made in the form a separate device containing a VAO3 control unit and a ferrite storage consisting of four type MSK-18 modules. Data is exchanged through the VAO3 control unit, equipped with two sets of input lines, for reception of the controlling word and data from the central processor and the input-cotput processor, and one set of output lines, for the transmission of information to the R122 processor. The modules of the storage device were connected in parallel and put into operation by the general controlling word. That unit sets the cycle of reference to the immediate-access storage on the basis of requests from the central processor of the input-output processor and establishes the priority of the input-output processor during simultaneous access.

#### FOR OFFICIAL USE ONLY

Technical Characteristics

Main memory capacity

Main memory access cycle time

Main memory word length

Word structure Memory operation 61 Kbites

2.5 microseconds

72 binary digits (18 binary digits

per module) .

8 bites with check digits

reading (readout of 8-bite word); recording (recording of 8-bite word

or part of word with regeneration of the initial content of the remainder

of the word)

The R212 control panel is intended for the operative control of the work of the M5100 computer complex and consists of a control unit, a "Konsul-260" printer, an operator's panel and power units.

Technical Characteristics

Information carrier Printing rate Line length

Set of characters

roll paper 200-250 mm wide

10 characters/s 106 charactees

The R512 tape unit performs the readout of information, given in the form of perforations on a 5-, 7- or 8-track punched tape, and refers the read information to the R122 processor, and also punches the data obtained from that processor. The unit consists of a control unit, an FS-1501 photoreader (CSSR), a PL-150 perforator and a power unit.

92

Technical Characteristics

Input rate Output rate 1500 lines/s 80 to 150 lines/s

The R630 card punch punches data obtained from the R122 processor on 80column punched cards. The punched cards advance in a channel and are punched by position. The R630 punch contains a reception unit for control readout of punched information from a punched card. The control is performed by the VAO7 control unit.

Technical Characteristics

Punching and readout rates Feed magazine capacity Receiving magazine capacity Number of receiving magazines 100+10 punched cards/minute at Teast 700 punched cards at least 500 punched cards

Henceforth the replacement of the R630 card punch by the PKPA80-3 (see 1.7) universal data preparation device is assumed.

15

The R610 punched card input device is intended for the input of data presented in the form of punched holes on 80-column punched cards. Punched cards move in the channel of the device by the narrow side, and the data are read by columns.

#### Technical Characteristics

| Readout rate                | 250, 500 punched cards/minute |

|-----------------------------|-------------------------------|

| Feed magazine capacity      | 1000 punched cards            |

| Receiving magazine capacity | 1000 punched cards            |

Printers. Provision is made for use of the ATsPU-128-3M alphanumeric printer or the DV-313 alphanumeric printer (Poland). Both devices print data from the R122 processor on perforated paper 420 mm wide. The number of different characters used in the printers is 96.

The printing rate of the ATsPU-128-3M is 360-440 lines/minute. The largest number of characters in a line is 128.

The printing rate of the DV-313 depends on the number of characters to be printed in a line. When short lines with not more than 32 characters are being printed, the rate remains 1520 lines/minute, and when full lines of 128 characteris are being printed, the rate diminishes to 190 lines/ minute.

Magnetic disk stores. All types of stores use as the carrier a detachable monodisk with a magnetic coating. The R412 store was used in preceding models of M5000 computers and is widely known by the users, and so its main characteristics are presented here only for comparison with the R414, R421A and R421B stores. In the R414 store, as in the R412 store, only one working surface of a disk is used at one time, that is, the disk must be halted for access to data on the other surface. The R414 store has a larger storage capacity than the R412. In each of those devices only one cassette with a disk can be installed, that is, those stores have a single electromechanical unit apiece. The R412 and R414 also contain electronic units that assure the performance by the devices of the required functions, and also power units.

# Technical Characteristics

| recimi | cal Characteristics                                           | R412                       | R414            |

|--------|---------------------------------------------------------------|----------------------------|-----------------|

| Number | of disks in a cassette                                        | 1                          | 1               |

| Number | of magnetic heads in a unit                                   | 1                          | 1               |

| Number | of tracks on one disk surface of recordings in a presentation | 1284                       | 128 6           |

| Number | of recordings in a presentation                               | 0.8'10° bites/s            | 1.6.10° bites/s |

| Number | of sectors in a track                                         | 20                         | 40              |

| Sector | capacity                                                      | 256 bites                  | 256 bites       |

| Useful | capacity of the working surface                               |                            | 6               |

|        | monodisk                                                      | 0.65·10 <sup>6</sup> bites | 1.30.10 bites   |

|        | otation rate                                                  | 960 rpm                    | 960 rpm         |

| Averag | e time of track access                                        | 200 millisec               | 150 millisec    |

|        |                                                               |                            |                 |

16

#### FOR OFFICIAL USE ONLY

The R421A and R421B stores differ substantially from the R412 and R414 stores both in the main indicators and in a design respect. A single device in the R421A execution has two storage units with corresponding electronic apparatus and a power source. In the R421B execution the device contains one storage unit. Both surfaces of the disk installed in the device are working surfaces, which in combination with the great capacity and the good time characteristics makes the R421 convenient and effective in the processing of large masses of data.

Technical Characteristics of a Separate Storage Unit

| Number of disks in a cassette                           |                              |

|---------------------------------------------------------|------------------------------|

| Number of working surfaces on a monodisk 2              |                              |

| Number of magnetic heads 2                              |                              |

| Track density 5                                         | tracks/mm                    |

| Number of tracks on a single disk surface 25            | 6<br>2·10 <sup>6</sup> bites |

| Useful capacity of the working surface of a monodisk 5. | 2.100 bites                  |

| Rate of disk rotation                                   | 000 rpm                      |

| Number of sectors in a track no                         | ot over 40                   |

| Recording and reproduction frequency 2.                 | 5.10 <sup>6</sup> bits/s     |

During work in the M5100 computer complex each electromechanical unit of the R421A store functions as a separate device in accordance with the assigned physical address.

The YeS-5012-01 magnetic tape store (Bulgaria) is intended for the recording, storage and reproduction of data on magnetic tape. The device consists of a tape drive, electronic apparatus that provides the recording and reproduction of data and operations of mechanism control and a power unit.

# Technical Characteristics

| Information exchange rate                     | up to 64 Kbites/s                 |

|-----------------------------------------------|-----------------------------------|

| Longitudinal density of information recording | 8 or 32 bits/mm                   |

| Number of tracks                              | 9                                 |

| Tape width                                    | 12.7 mm<br>2·10 <sup>8</sup> bits |

| Cassette capacity                             |                                   |

| Tape velocity                                 | 2+0.1 m/s                         |

| Power consumption                             | not over 2.5 kV·A                 |

#### 1.4. Data Preparation System

Two important aspects in the technology of processing accounting and statistical information are connected with the data carriers: the first is data storage and the second is the preparation of primary data and its input into the computer.

In the area of application of type M5000 computer complexes punched cards have long been the dominant data carrier both for the storage and for the input of primary data. The volume of work done by standard computer and

17

data processing centers can be determined from the quantity of punched cards processed monthly--(400-500)·10<sup>3</sup>. About 50 percent of them require fairly long storage--6 months or more. Punched card storage involves great inconveniences. Finally, large volumes of data on punched cards lead to a considerable expenditure of a material in short supply--paper for their manufacture. For these reasons the further application of punched cards as data carriers is not promising.

In all models of the type M5000 computer complex, including the M5100, the magnetic disk is the main data carrier in the sense of data processing and storage. The R412, R414 and R421 magnetic disk stores with replaceable cassettes assure fairly reliable and convenient storage of large masses of data and at the same time provide immediate access to the data. Besides the devices and cassettes delivered with the basic set of equipment of the complex, the user can acquire cassettes containing disks separately in a quantity assuring data storage in the necessary volume. Along with that, in the M5010 and M5100 complexes there is the possibility of storing data on magnetic tapes. Thus, with the application of computer complexes of the M5000 type the work with punched cards is reduced to just the preparation of primary data or can be eliminated completely.

In the M5100 complex the question of preparation of primary data without using punched cards can be solved by using the R810 data preparation system.

The R810 data preparation system is being produced by industry at the present time and can be acquired by a user. The system is intended for the keyboard input of data from primary documents on replaceable magnetic disk stores used in the M5000, M5010 and M5100 complexes. The application of the R810 system for the preparation of primary data instead of punched card equipment can increase labor productivity on data preparation by 25-30 percent through a greater degree of automation of data transfer from keyboard to carrier, a higher rate of execution of duplication, skipping and recording of nonsignificant zeroes, simplicity of error correction and great reliability of the apparatus. The input of data stored on magnetic disks in the autonomous R810 system also gives a considerable saving of machine time, as it is done several times more rapidly than the input of the same volume of data from punched cards.

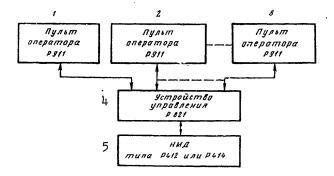

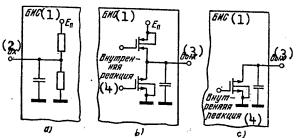

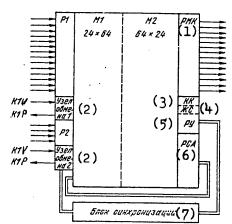

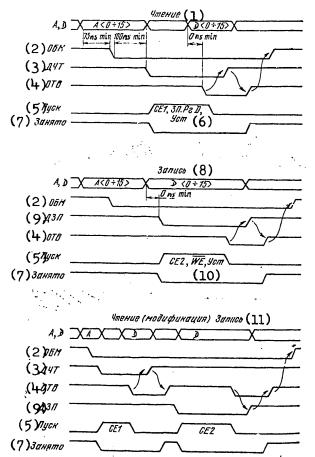

The R810 system (Fig 1.3) is an autonomous system that assures data input from several keyboards working simultaneously and data storage on a replaceable magnetic disk. The system can have from 1 to 8 keyboards, each of which together with the control apparatus and the indication system represents an R911 operator panel. That panel has a desk-top design. The R821 control unit of that system is intended for intermediate storage, primary processing and the monitoring of data input from keyboards, coordination of the work of the panels and control of the store. An R412 or R414 can be used as the store.

18

Each of the operators of an R810 system is presented the possibility of the input by character of recordings with a length of 1 to 224 alphanumeric characters, constituting the lines of the primary document. The recordings are disposed on a magnetic disk in the zone allocated for the operator. Each sector of the disk in the zone allocated to the operator can contain from 1 to 15 recordings with a total length of not more than 256 bites. The total capacity of one disk surface is distributed as a function of the number of operator panels. Recordings are made on a disk in the internal code of the M5100 computer complex and can be used directly for processing after they have been stored.

Fig 1.3. Structure of the R810 data preparation system.

1, 2 and 3 -- R911 operator panel

4 -- R821 control unit

5 -- R412 or R474 magnetic disk store

The work of the operators is automated by means of format programs consisting of a sequence of 8-bit code combinations, each of which characterizes a separate character in the recording. The format programs are stored in the process of the work in the storage of the R821 control unit and can be input from the R911 operator panel or from the store itself. The storage in the magnetic disk store of up to 200 format programs is provided for in the system. The functions of format programs include the monitoring and primary processing of input recordings, including:

- --the monitoring of recordings by means of control sums within the limits of a single recording;

- -- the monitoring of the length of fields by means of separative information;

- --monitoring the type of introduced character (figure, letter of the Russian or Roman alphabet, or special sign);

- --automatic filling of all positions of the field by the code "space";

- --automatic duplication of fields;

- -- automatic recording of nonsignificant zeroes of the indicator.

19

The R911 operator panel contains an alphanumeric keyboard corresponding to type 2 according to All-Union State Standard 14289-69, with a total number of 94 different characters. Besides the alphanumeric keyboard there is a separate keyboard for the input of only digital information by the "blind" method, corresponding to All-Union State Standard 15816-70.

Visual monitoring of the work of the operator and of the system as a whole can be accomplished by means of an indication table on which provision is made for the indication of an input character, orders of the format program, addresses of recordings in the magnetic disk store, the state of apparatus of the system, etc. Failure in the work of the system or apparatus through the fault of the operator is signalized by means of a sound signal.

The above examined brief technical characterization of the R810 data preparation system makes it possible for the user to become acquainted with one of the most promising methods of data preparation. The introduction of this system will lead in the end to gradual displacement of punched cards as information carriers, and consequently of punched card equipment.

In the M5100 computer complex provision is made for the use of traditional data carriers--punched cards, in view of the fact that punched card equipment is still widespread at the present time, the technology of punched card processing is well organized, but the replacement of punched card equipment and the equipping of computer centers with equipment for the preparation of data on magnetic carriers can be done gradually, in proportion to the production of a sufficient quantity of the equipment. Therefore in the set of spare parts the user receives equipment for the preparation of data on punched cards of the PKPA80-1 type, which accomplishes the punching and primary monitoring of data given by the operator by means of a keyboard.

In the M5100 computer complex provision is made for the use of punched tape equipment, but equipment for the preparation of data on punched tape is not delivered with the set, but can be acquired by the user separately. When it is necessary to store and frequently use data on perforated tape the data can be prepared by means of punched card equipment. In that case the data must be re-registered from punched cards to punched tape by means of programs of the operational system.

# 1.5. Technical Servicing of the Complex

Technical servicing of the complex includes the conducting of regular prophylactic and maintenance work, and also periodic verification of the working capacity of the complex. All types of work connected with technical servicing are done by means of hardware and software intended for that purpose.

The periodicity and volume of regular prophylactic work is provided for by the technical domumentation of the equipment in the complex and assured, where that is possible, by special instruments constituting the set of

20

#### FOR OFFICIAL USE ONLY

of service apparatus. The service apparatus is also intended for maintenance work. The single structural and elementary base of logical devices and units of the complex permits using a small set of instruments to seek out and eliminate malfunctions in the logical units. Any standard replacement element can be inspected by means of instruments in the set of service apparatus: the SAO1 stand or the SAO2 stand. The SAO1 stand is used for the inspection of some special standard replacement elements, and the SAO2 stand for the inspection of standard replacement elements containing logical apparatus.

Very important in technical servicing are inspection of the working capacity and in the case of appearance of a failure, seeking out the place of the malfunction. Software and hardware also are provided for that work in the complex.

Operative monitoring of the working capacity of separate devices in the complex as a whole is done by means of special test and control programs. A system of test programs is delivered along with the software of the complex and embraces all the devices in the specific configuration of the complex. The main task of the test programs is verification of working capacity with maximum embrace of the functional possibilities of the component parts of the complex. However, the test programs represent the first stage in the diagnosis of failures, as they permit distinguishing the separate failed parts of the complex on the basis of data printed in the reports of test programs on the printer of the R212 control panel.

Another type of operative monitoring is the solution of check problems, which consist in programs working in regimes very similar to the regimes of fulfilment of real problems. Verification by means of check problems requires considerably more time and is recommended upon the startup of a complex after large amounts of repair or maintenance work. Check problem programs are also delivered with the software of the complex.

The methods and means of seeking out malfunctions of separate parts of a complex also are indicated in the technical documentation of the equipment. The apparatus base for seeking out the places of failures consists of built-in panels that assure autonomous working regimes of the devices and units. In most cases a faulty device can be effectively disconnected from the system in order to do repair work without halting the remaining part of the complex.

Very complex logical devices, such as the R122 processor, the magnetic disk store control unit, etc, have a fairly developed manual control apparatus, intended for the diagnosis of defects. In particular, the R122 processor assures all the working regimes necessary for the inspection and regulation of the R140 immediate-access storage in a complex without special testing apparatus.

A partially automated system for finding defects has also been developed for the M5100 computer complex, one that compiles special programs with

21

with fixed data and a procedure for their use. The system can use punched cards or tapes or magnetic disks as information carriers. The main task of an automated system for finding defects is effective determination of the character and place of a defect in a very complex logical device, the R122 processor, but it is also useful in finding defects in other devices of a complex.

# 1.6. Brief Characterization of the Software

The software of the M5100 computer complex, delivered with the equipment, consists of a disk operating system, test programs and check problem programs.

The M5100 disk operating system (DOS) is the basic software component intended for the effective use of the hardware of the complex in all its applications. The DOS consists of a group of programs that give the user the means to compile working programs and run them on the machine, and that also accomplish control of the equipment during the running of those programs. The DOS programs participate in the work of the complex both during the preparation and running of programs of the user and during the running of check problem programs and some test programs.

Test programs and check problem programs have a narrower application and are used only to verify the working capacity of hardware of the complex (see 1.5).

The software is delivered to the user in the form of magnetic disk recordings and corresponding technical documentation.

The M5100 disk operating system is a single one for all alternatives of execution of the complex and includes the programs needed for control of devices the complex in any composition. The DOS in the form in which it is delivered to the user along with the equipment of the complex can be used by him without the introduction of any sort of changes. However, in the general case the DOS in that form is not adapted in the best manner to the specific configuration of the equipment and to the class of problems solved by it. Therefore the user is presented means of generation that permit forming DOS alternatives, that is, so-called DOS generations that are most suitable in solving problems of a definite class with the use of a specific composition of devices. In proportion to the inclusion in the complex of devices of other types not in the main composition: adapters for communication with other electronic computers, video terminals, etc, in the DOS delivered to the user programs assuring the use of the new devices will be included. DOS programs are characterized by a modular structure, which also assure the possibility of forming the required DOS alternatives.

The external carrier of disk operating system programs is the magnetic disk. Magnetic disk stores of any type from the number of devices available in a specific variant of execution of the complex can be used as the DOS carrier in the process of the work.

22

FOR OFFICIAL USE ONLY

Ē

1

The main tasks of disk operating systems are curtailment of the time from the moment the problem is formulated to the obtaining of the results of its solution and increase of the effectiveness of use of equipment of the complex.

Curtailment of the time from the formulation of the problem until the obtaining of the result is achieved because the M5100 DOS presents means of programming in symbolic source languages of a different level: Kobol, RFG, PL/1, Assembler and, in addition, contains a number of programs intended for service work in the adjustment and documentation of programs of the

Increase of the effectiveness of use of equipment of the complex is achieved by organizing, by means of the disk operating system, packet processing as the principal method of running programs of the user, and a multiprogram working regime of the complex, in which up to three programs of the user are run independently and simultaneously.

Packet processing consists in this, that all the work done, consisting of one or several programs, is formulated in the form of tasks containing controlling information for an operating system, and also programs and data relating to programs if they are required. Such tasks are grouped in packets and form an input flow of tasks for the system. The transition from fulfilment of one task to another occurs by means of the disk operating system automatically upon completion of the next task. The application of packet processing improves the use of machine time, reduces downtime of the equipment in the intervals between the running of separate programs and thus reduces the volume of work done by the operator manually.

Packet processing does not, however, exclude the possibilities of starting and running single programs.

Multiprogram work. In the M5100 computer complex, in contrast with the M5000 computer complex, a multiprogram regime of work has been realized. That regime is organized by the formation of a fixed number of sections of the immediate-access memory allocated for programs of the user. The number of sections (from 1 to 3) is established during DOS generation for the specific configuration of the equipment. The multiprogram regime of work adopted in the M5100 DOS is characterized by the fact that for each section of the immediate-access memory a certain set of input-output equipment is allocated, that is, all the means of the complex are fictitiously divided into parts constituting as it were independent simultaneously working computers.

In a multiprogram work regime in each section its own flow of tasks is run independently of the flows of tasks of other sections. Within the limits of each flow of tasks all the tasks are run successively, one after the other. Between the sections of the immediate-access memory and, therefore, the programs in the sections, a rigid order of priority is established

23

#### FOR OFFICIAL USE ONLY

which also determines the distribution of time of the central processor in the multiprogram regime of performance of tasks.

The volume of immediate-access memory allocated to a section is not fixed and can be established with consideration of the class of the problems to be solved, starting from some minimum volume set by the operating system to assure the functioning in the section of part of the disk operating system controlling programs.

From the point of view of the user, each section with the input-output devices allocated for it can be regarded as a separate computer, working in a regime of packet processing. Any user program can be run in any section if the volume of the immediate-access memory and the composition of the equipment allocated for that section satisfy its requirements.

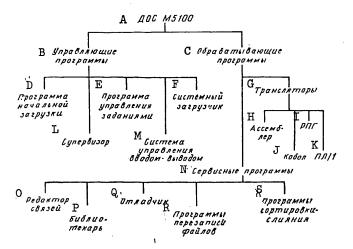

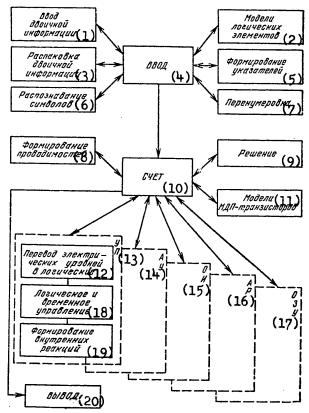

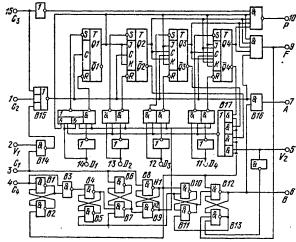

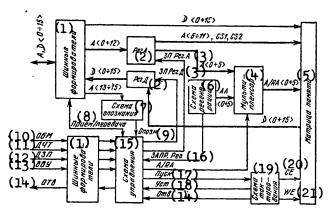

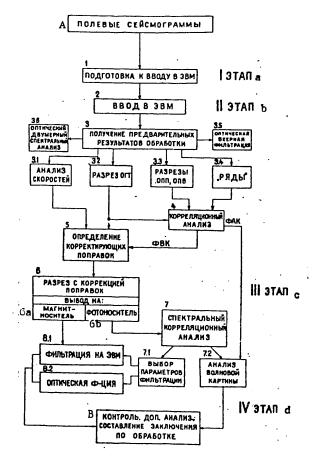

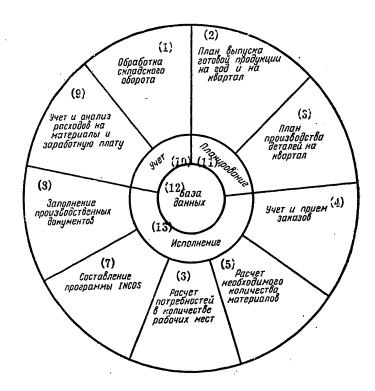

Disk operating systems programs are divided according to functional designation into two groups: controlling and processing (Fig 1.4).

Controlling programs accomplish the distribution of resources of the system, organization of the uninterrupted running of programs, control of the work of equipment and monitoring of its functioning, and also assure the parallel work of the processor and input-output devices. A portion of the controlling programs is constantly in the immediate-access memory and participates in the running of any disk operating system processing program or user program.

The initial loading program acts at the moment of initiation of work of the system and is intended for readout from the resident disk and disposition in the immediate-access memory of that part of the controlling program which must constantly be in the memory in the process of running other programs.

The supervisor is a part of a controlling program and is intended for monitoring the execution of the working program and the control and monitoring of the functioning of equipment of the complex.

The main function of the supervisor is to distribute the time of the central processor in a multiprogram work regime by starting from the activity and priority of the section in which the program is run.

A section is considered active for which the immediate-access memory has been distinguished and which contains a program ready for execution. The supervisor plans the time of the central processor by surveying the sections in the order of decreasing priority. Control is transferred to the program that is in the first active section, discovered during their successive survey. That program can be run until a section with a higher priority becomes active, or in the program itself a situation develops in which its continuation is possible only after the end of some event: completion of the input-output operation, expiration of a given time interval, etc. In that case the control is transferred to the program contained in

24

an active section with a lower priority. In the absence of active sections the supervisor transfers the computer system into a waiting mode of operation.

Other functions of the supervisor include the planning of input-output operations, the loading of programs in the immediate-access memory, the execution of procedures in the completion of programs, the organization of communications with the operator of the system, the creation of check points in working programs, the correction of equipment malfunctions, etc. All these functions can make use of programs run in each section.

The functioning of the supervisor starts directly after performance of the procedure of initial loading. In that stage of the work of the operating system the supervisor loads in the immediate-access memory and triggers the program of control of disk operating system tasks for the purpose of organizing the start of the execution of tasks. Later, during the running of other disk operating system programs or user programs, the supervisor obtains control through the interrupt system. The interruption of a program being run and transfer of control to the supervisor in some cases occur asynchronously in relation to the program being run, as, for example, during malfunctions of equipment during the running of a program. The transfer of control to the supervisor for the purpose of execution of prescribed functions can also occur upon requests of the program being run at points specified in the program. For that purpose macroorders of the supervisor that define the required functions are included in the starting program. After translation into the machine language the working program at the points of arrangement of the macroorders contains orders to refer to the supervisor that cause program interruptions, that is, transfer of the supervisor's control of the programs.

The program of task control is intended for the organization of packet processing. The task of this part of the controlling program consists in the organization of the reception of tasks and their subsequent execution, and in the organization of the preparation and start of separate recording programs. In that case the program of task control establishes the working regime of the disk operating system, designates the physical input-output devices in accordance with the logical numbers of the devices in the programs, etc. In the execution of its functions the program of task control uses information contained in special operators of task control. The necessary operators of task control are selected by the programmer during compilation of the packet of tasks. The operator servicing the complex can also act on the course of execution of the flow of tasks by introducing through the control panel printer directives of task control, similar to the operators controlling tasks included in a packet.

The task control program is stored in the system library of absolute modules on a resident disk and is called into the immediate-access memory by the supervisor after the initial loading, completion of the task or part of it, after abnormal completion of the task or according to the requirement of the operator servicing the complex. This program is run in each section in the

25

TOK OLLTOTAT OPE ONTI

Fig 1.4. Composition of the M5100 disk operating system.

- A -- M5100 DOS

- B -- Controlling programs

- C -- Processing programs

- D -- Initial loading program

- E -- Task control program

- F -- Systems loader

- G -- Translators

- H -- Assembler

- I -- RPG

- J -- Kobol

- K -- PL/1

- L -- Supervisor

- M -- Input-output control system

- N -- Service programs

- 0 -- Communication editor

- P -- Librarian

- Q -- Adjuster

- R -- File re-recording programs

- S -- Sorting and merger programs

same regions of the immediate-access memory as the problem programs. The work of the task control program is concluded by transfer of control to the supervisor with the requirement of loading of the next problem program of the packet. Thus in processing the flow of tasks in each section the work of the task control program is alternated with the next program of the packet.

The input-output control system is intended for the organization of the procedure of reference files on external carriers. Modules of the input-output control system are stored in the system library on a resident disk and are switched into the working program in the stage of preparation and execution if the initial problem program contains operators requesting the performance of definite functions of the input-output control system.

The system loading consists of a program that performs the loading of working programs in the immediate-access memory of the libraries of absolute modules by the moment of their execution. The system loader uses both the task control program, which in that case performs the loading and start of

26

# FOR OFFICIAL USE ONLY

the first program module, and also the same working programs in which provision is made for loading of program phases by means of macroorders of the supervisor.

The processing programs are intended for the preparation of programs for execution, organization of program storage and the execution of procedures often used by problem programs.