JPRS L/9826 6 July 1981

## **USSR** Report

# CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY

(FOUO 16/81)

Excerpts from the Journal 'COMPUTER TECHNOLOGY

OF THE SOCIALIST COUNTRIES'

FOR OFFICIAL USE ONLY

#### NOTE

JPRS publications contain information primarily from foreign newspapers, periodicals and books, but also from news agency transmissions and broadcasts. Materials from foreign-language sources are translated; those from English-language sources are transcribed or reprinted, with the original phrasing and other characteristics retained.

Headlines, editorial reports, and material enclosed in brackets [] are supplied by JPRS. Processing indicators such as [Text] or [Excerpt] in the first line of each item, or following the last line of a brief, indicate how the original information was processed. Where no processing indicator is given, the information was summarized or extracted.

Unfamiliar names rendered phonetically or transliterated are enclosed in parentheses. Words or names preceded by a question mark and enclosed in parentheses were not clear in the original but have been supplied as appropriate in context. Other unattributed parenthetical notes within the body of an item originate with the source. Times within items are as given by source.

The contents of this publication in no way represent the policies, views or attitudes of the U.S. Government.

COPYRIGHT LAWS AND REGULATIONS GOVERNING OWNERSHIP OF MATERIALS REPRODUCED HEREIN REQUIRE THAT DISSEMINATION OF THIS PUBLICATION BE RESTRICTED FOR OFFICIAL USE ONLY.

JPRS L/9826 6 July 1981

## USSR REPORT

## CYBERNETICS, COMPUTERS AND AUTOMATION TECHNOLOGY

## (FOUO 16/81)

# EXCERPTS FROM THE JOURNAL 'COMPUTER TECHNOLOGY OF THE SOCIALIST COUNTRIES'

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980

## CONTENTS

| COUNTRIES'                                                                                           | 1  |

|------------------------------------------------------------------------------------------------------|----|

| Computer Technology of the Socialist Countries                                                       | 3  |

| Development Stages of the Small Computer System                                                      | 5  |

| SM-52/10 Small Computer                                                                              | 10 |

| Modular Concept in Developments of GDR Data Preparation Units and Terminals for YeS and SM Computers | 14 |

| Development of Small Computers in Cuba                                                               | 20 |

| Principles of Building Multilevel Automated Control Systems                                          | 24 |

| SM-1 and SM-2 Control Computer Complexes                                                             | 31 |

| Terminal Interface Machine Based on the SM-3 Computer                                                | 39 |

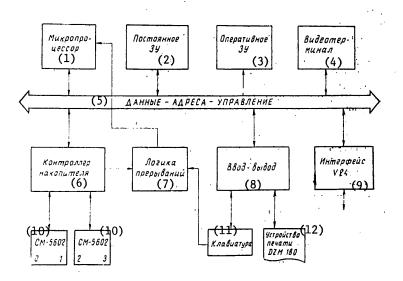

| Microcomputer Application in Laboratory Gas Chromatography                                           | 44 |

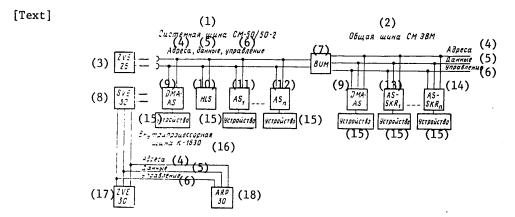

| Organization of Multiprocessor Operation Based on SM-50/40-1 Microcomputer Modules                   | 52 |

- a - [III - USSR - 21C S&T FOUO]

## FOR OFFICIAL USE ONLY

## FOR OFFICIAL USE ONLY

| SM-50/20-2 Microcomputer                                                            | 57 |

|-------------------------------------------------------------------------------------|----|

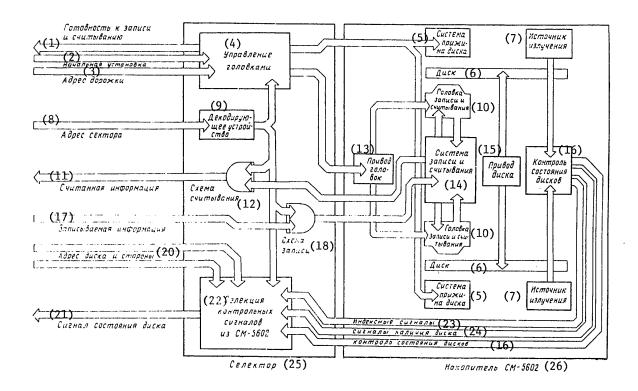

| Floppy Disk Storage Units                                                           | 66 |

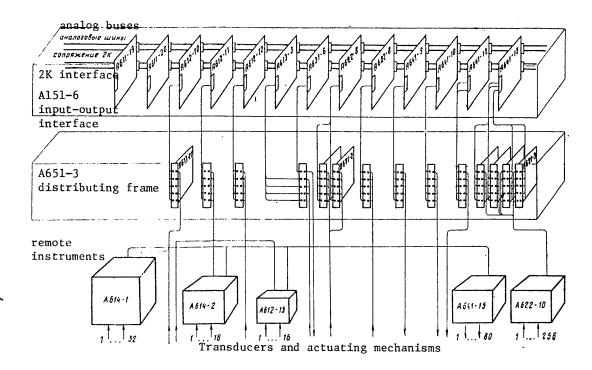

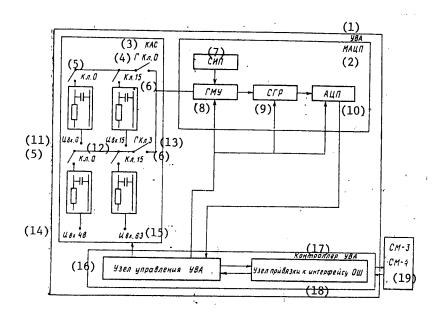

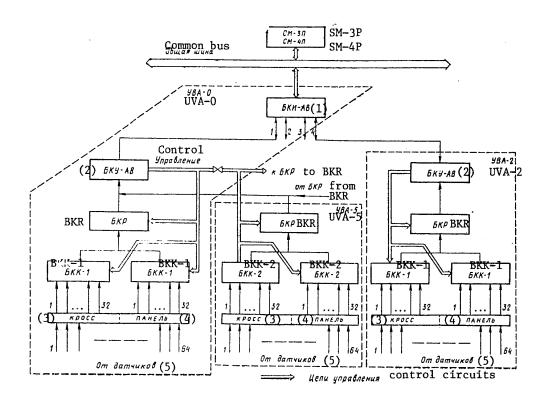

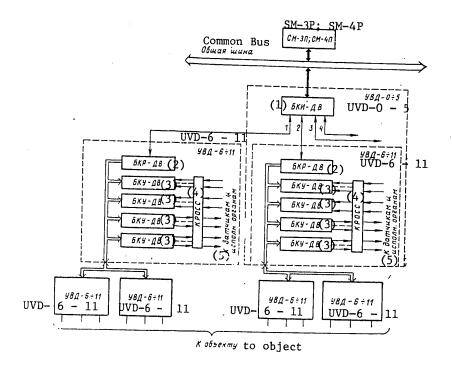

| Units for Communication With the Object of Control Computer Complexes in the SM EVM | 72 |

| FOBOS Operating System for Small Computers                                          |    |

| IRIS Data Base for a Hierarchic Multimachine Complex                                | 86 |

| Computer Instruction Interpreter                                                    | 90 |

| SM-5304 Magnetic Tape Storage Unit                                                  | 92 |

| New Hardware for the System of Small Computers                                      | 96 |

## FOR OFFICIAL USE ONLY

TABLE OF CONTENTS FROM COLLECTION 'COMPUTER TECHNOLOGY OF THE SOCIALIST COUNTRIES'

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980 (signed to press 17 Nov 80) p 155

[Table of contents from book "Competer Technology of the Socialist Countries", a collection of articles, edited by M. Ye. Rakovskiy, Izdatel'stvo "Statistika", 16,000 copies, 168 pages]

| [Te | xt] Contents                                                                     | Page |

|-----|----------------------------------------------------------------------------------|------|

| Pre | face                                                                             | 3    |

| I.  | International Cooperation between the Socialist Countries in Computer Technology |      |

|     | Naumov, B. N. Development Stages of the Small Computer System                    | 5    |

|     | Gantner, Ya. The SM-52/10 Small Computer                                         | 10   |

|     | Merkel, G. and Jungnickel, H. G. The Modular Concept in Developments             |      |

|     | of GDR Data Preparation Units and Terminals for YeS and SM Computers             | 13   |

|     | Karrasko, L. H. Development of Small Computers in Cuba                           | 19   |

|     | Sedegov, R. S.; Bashko, V. A. and Shipulin, A. M. Principles of                  |      |

|     | Building a Multilevel ASU                                                        | 23   |

| II. | Computer Hardware                                                                |      |

|     | Kostelyanskiy, V. M. and Rezanov, V. V. The SM-1 and SM-2 Control                |      |

|     | Computer Complexes                                                               | 30   |

|     | Beiner, E. T.; Treis, P. P. and Yakubaitis, E. A. The Terminal                   | -    |

|     | Interface Machine Based on the SM-3 Computer                                     | 38   |

|     | Fehre, W. and Kummer, M. Microcomputer Application in Laboratory Gas             |      |

|     | Chromatography                                                                   | 4.2  |

|     | Gus'kov, V. D.; Kabanov, N. D.; Kravchenko, V. S. and Shkamarda, A. N.           |      |

|     | Organization of Multiprocessor Operation Based on SM-50/40-1 Micro-              |      |

|     | computer Modules                                                                 | 49   |

|     | Giebler, H. and Lauermann, M. The SM-50/50-2 Microcomputer                       | 54   |

|     | Pieszko, A. and Gwizdala, B. Floppy Disk Storage Units                           | 63   |

|     | Sokolov, A. Ya.; Sopochkin, L. A.; Strashun, Yu. P. and Sergeyev, L. A.          |      |

|     | Computer-to-Object Adapter for SM Control Computer Complexes                     | 69   |

|     | Lyubimov, A. G. Power Supplies for Minicomputers                                 | 78   |

1

#### FOR OFFICIAL USE ONLY

| III. | Computer Software                                                     |     |

|------|-----------------------------------------------------------------------|-----|

|      | Machacka, I. The FOBOS Operating System for SM Computers              | 87  |

|      | Prachenko, V. D.; Filinov, Ye. N. and Khristochevskiy, S. A.          |     |

|      | The IRIS Data Base for a Hierarchic Multimachine Complex              | 93  |

|      | Vigdorchik, G. V.; Vorob'yev, A. Yu. and Rostokin, B. I. Discrete and |     |

|      | Continuous Process Simulation System for SM Computers                 | 96  |

|      | Kratochvil, E. and Chlouba, Ya. PROTABDecision Table Translators      |     |

|      | for YeS Computers                                                     | 103 |

| IV.  | Application of Computer Facilities                                    |     |

|      | Landau, I. Ya. and Vagner, E. N. Automated Design Stations and a New  |     |

|      | Approach to Computer Aided Design                                     | 111 |

|      | Rusnak, Ya.; Gorsky, I. and Smolak, L. Creating an ASU for a Multi-   |     |

|      | purpose Hospital Based on a Minicomputer                              | 116 |

|      | Ivanov, D. and Kharalanov, B. Automated System for Real-Time          |     |

|      | Production Management in Food Industry Enterprises                    | 126 |

|      | Szekely, T. and Shatalina, L. S. ASU for the Association              |     |

|      | "Mosavtotekhobsluzhivaniye" [Moscow Motor Vehicle Maintenance]        | 131 |

| V.   | Information on New Computer Facilities                                |     |

|      | Mirgos, L. The SM-5304 Magnetic Tape Storage Unit                     | 139 |

|      | Simeonov, D. and Iliyev, B. Computer Instruction Interpreter          | 142 |

|      | New SM Computer Hardware                                              | 144 |

|      | Abstracts                                                             | 157 |

COPYRIGHT: Izdatel'stvo "Statistika", 1980

8545

CSO: 1863/157

#### FOR OFFICIAL USE ONLY

#### COMPUTER TECHNOLOGY OF THE SOCIALIST COUNTRIES

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980 (signed to press 17 Nov 80) pp 2-4

[Annotation and preface from book "Computer Technology of the Socialist Countries", a collection of articles, edited by M. Ye. Rakovskiy, Izdatel'stvo "Statistika", 16,000 copies, 168 pages]

[Text] This international collection deals with the problems of research, development, application and operating experience of computer hardware and software developed under the agreement on cooperation in computer technology between the socialist countries: the NRB [People's Republic of Bulgaria], the VNR [Hungarian People's Republic], the GDR [German Democratic Republic], the PNR [Polish People's Republic], the Republic of Cuba, the SRR [Socialist Republic of Romania], the ChSSR [Czechoslovak Socialist Republic] and the USSR.

Treated in this collection of articles are general development problems of the small computer system (SM EVM), specific hardware and systems for the SM EVM, software for the SM EVM and problems of application of SM EVM facilities in hierarchic multimachine complexes, computer networks and ASU's.

The collection is intended for specialists engaged in developing and using facilities of the YeS [unified system] and SM computers.

#### Preface

The level of automation of processes in the various spheres of social production is largely determined by the presence of mini and micro computers which thanks to microelectronic technology, advanced software, simplicity of maintenance and low cost are gaining more and more fields of application and becoming the most widespread class of computers.

Characteristics of the small ...computer system (SM EVM), developed in the socialist countries, were determined primarily by the needs of the countries for creating automated control systems (ASU), automating scientific experiments, automating design, and using computers in the nonindustrial sphere. The SM ...computer development program presupposes simultaneous development of hardware and software in the form of problem oriented complexes that will encompass the various fields of application.

#### FOR OFFICIAL USE ONLY

Considering the large number of developments in the socialist countries, the experience of applying small computers in various fields and the great interest in this class of machines, this, the eighth issue of the collection "Computer Technology of the Socialist Countries," is devoted to this theme.

This collection includes both articles dealing with general problems of SM computer development in the socialist countries, and articles on specific SM computer hardware and systems (SM computer complexes, SM computer power supplies, floppy disks in SM computers and others) and software. Articles in the collection show the application of SM computers in hierarchic multimachine complexes, computer networks, automated control systems and for automation of design. The collection also includes articles on the SM-50/50-2, SM-50/10-1 and SM-50/40-1 microcomputer systems.

Without question, even a topical collection on small computers does not cover fully all the tasks and efforts underway in the cooperation of development of mini and micro computers, but from time to time we hope to return to this topic and publish articles on the most varied aspects of development and application of small computers and on the problems of their standardization, operation and maintenance.

The Editors

COPYRIGHT: Izdatel'stvo "Statistika", 1980

8545

CSO: 1863/157

FOR OFFICIAL USE ONLY

DEVELOPMENT STAGES OF THE SMALL COMPUTER SYSTEM

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980 (signed to press 17 Nov 80) pp 5-10

[Article by B. N. Naumov, corresponding member of the USSR Academy of Sciences (USSR), from book "Computer Technology of the Socialist Countries", a collection of articles, edited by M. Ye. Rakovskiy, Izdatel'stvo "Statistika", 16,000 copies, 168 pages]

[Text] The small computer system (SM EVM) is a modular complex of hardware and software intended primarily for use in real-time systems and organically tied to the requirements that the user dictates. Therefore, the selection of characteristics and determination of the nomenclature of the modules of control computer complexes (UVK) involves profound and broad analysis of user requirements.

The small computer system is being developed in several stages. The first phase of the small computer hardware development plan specified development of a functionally complete set of hardware during the period from 1976 through 1980 for configuration of various automated systems. This task was essentially completed in 1979. Within the small computer system, about a hundred different devices representing a functionally complete set have been developed, tested and are in production; this set enables building automated systems of varying complexity.

Four models of processors with different throughput, the SM-1P, SM-2P, SM-3P and the SM-4P (Poland, Cuba, Romania, USSR and CSSR), and a series of main memories and devices for systems complexing (Bulgaria, Hungary, Poland, USSR and CSSR) have been developed under the first phase of the program; these devices enable building systems with a variable configuration and wide range of characteristics. The small computer system includes a large set of peripherals: external storage on fixed and removable magnetic disks and on floppy disks, input and output devices operating with perforated tape and cards, serial and parallel printers, alphanumeric and graphic displays, equipment for transmitting data over telephone and telegraph channels, data preparation devices and devices for communication with an object.

The following table shows the number of devices by individual groups of equipment that successfully passed joint tests in the period 1977 to 1979 (second-phase devices that were tested in 1979 are also included in the table):

#### FOR OFFICIAL USE ONLY

| Equipment Groups                                          | <u>BU</u> | HU | GDR | <u>Cuba</u> | <u>P0</u> | RO | USSR | CSSR | <u>Total</u> |

|-----------------------------------------------------------|-----------|----|-----|-------------|-----------|----|------|------|--------------|

| Processors                                                | _         | _  | 2   | 1           | 1         | 1  | 4    | 2    | 11           |

| Main Memories                                             | 1         |    | -   | -           | 1         | -  | 2    | 3    | 7            |

| External Storage Devices and<br>Controllers for Them      | 7         | 4  | _   | -           | 5         | _  | 2    | 3    | 21           |

| Input-Output Devices and<br>Controllers for Them          | 1         | 6  | 5   | _           | 6         | 2  | 2    | 8    | 30           |

| Terminals and Terminal Stations                           | -         | 5  | 1   | 1           | 1         | -  | 1    | 1.   | 10           |

| Devices and Terminals for<br>Communication with an Object | _         | -  | _   | _           | -         | _  | 2    | 2    | 4            |

| Data Transmission Devices                                 | -         | 3  | -   | -           | -         | -  | 2    | 4    | 9            |

| Data Preparation Devices                                  | 1         | _  | 2   | -           | -         | -  | -    | 1    | 4            |

| Inter- and Intrasystem<br>Communication Devices           | -         | -  | -   | -           | -         | _  | -    | 3    | 3            |

| Other Devices                                             | -         | -  | -   | 1           | -         |    | -    | 1    | 2            |

| Totals by Country                                         | 10        | 18 | 10  | 3           | 14        | 3  | 15   | 28   | 101          |

Also tested in 1977-1979 were 28 software components--operating systems and application program packages.

The traditional sequence of developing software after completion of hardware development often leads to obsolescence of a system even before it is put into operation. The small computer system development plans specify simultaneous development of hardware and software, as well as control systems based on them in the form of problem-oriented complexes (POK). In the process, the technical level of control systems based on the small computer system is being raised considerably through the organization of distributed data processing in control systems using several compatible small computers. This raises system reliability and viability considerably, and in addition, by bringing out and localizing autonomous control loops, makes it possible to simplify and accelerate program writing and debugging which results in reducing the time needed to put a system into operation.

A large number of systems for various users based on one or several, if necessary, problem-oriented complexes are developed by varying the structure of hardware and software and elaborating the software with specific applied tasks. The most labor-intensive tasks of tying the hardware needed to the basic software under the concrete modes and conditions of operation are handled by the skilled specialists of the leading systems organizations and organizations-developers of the hardware when the problem-oriented complex is created.

Development of the first phase of the small computer system has led to a significant improvement in the technical level of the small computers produced by the industry of the socialist countries. The physical sizes of complexes have been sharply reduced (to about one-fifth of the previous size), cost has been reduced considerably (to about one-half of the previous cost), and reliability indicators

#### FOR OFFICIAL USE ONLY

have improved (about twofold). This was achieved by shifting to microprogram control in processors, using microcircuits with a higher degree of integration and improved connecting pins, using small power sources and compact peripherals and by raising the manufacturability of the designs.

In 1977, the "Concept for Development of the Small Computer System (Second Phase)" was adopted; the basic directions for development were formulated in it. And in 1978, the "Preliminary Design, Plans and Specifications for the Second Phase of the Small Computer System" was accepted. Elaboration of the "Development Program for the Second Phase of the Small Computer System" is nearing completion. The concept, design and program set several goals. The major goals are:

fuller satisfaction of national economic demand for, and elimination of the shortage of, small computer hardware to build automated systems in various sectors and to perform autonomous design operations;

creation of the prerequisites for mass introduction of this class of hardware into the national economy;

improvement of the technical and economic indicators for the hardware, expansion of its functional capabilities and enhancement of flexibility, bringing the technical level of the small computer system closer to the level of the best modern small computers; and

raising the economic effectiveness of utilization of computer equipment.

Proceeding from these goals, the concept design and program for developing the second phase of the small computer system envision a substantial expansion of the computer nomenclature with regard to specialization in the hierarchy of hardware, including in teleprocessing network systems.

The element base for this phase of computers will consist of three microprocessor series (sets) of large-scale integrated circuits distinguished for speed of response and power consumption. The sets are standardized in design and will have the necessary elements for matching of signal levels.

First phase models of the small computer system using second phase microprocessors will basically have the appearance of systems with processors-expanders. In these systems, the new system processors will be compatible with those of the first phase computers, the capability of realizing certain software functions by hardware will be provided, the central processor will be unloaded by having the processors-expanders perform a number of functions (input-output processors, file management processors, communications processors in multimachine systems, specialized processors, for example for Fourier transformations, and others). Using specialized processors in control and computer complexes will make it possible to increase average throughput in certain classes of problems by an order of one-two.

A substantial portion of the nomenclature of control devices—controllers for the peripherals will also be realized on the basis of microprocessors. In the process, the same functional modules may be used for operation with different peripherals. To perform specific prescribed functions, these modules will be programmed at the level of microinstructions or conventional instructions of microprocessors. This will make it possible to standardize hardware, reduce hardware outlays for realization of devices with fixed logic, increase flexibility during system design and implementation and raise reliability considerably.

In the second phase of the small computer system, it is planned to develop superior models that have considerably higher throughput (several millions of operations per second with a main memory capacity up to 1-2M bytes) than first phase models, with advantageous economic indicators. These models are intended for use in the upper levels of control systems operating in real time, where it is necessary to provide for acquisition and processing of large information streams or solving complex problems for which the throughput of conventional small computers is insufficient and the application of large computers is inefficient. These are, for example, systems for complex scientific research, systems for monitoring and testing complex objects and systems for control of fast-flowing processes.

The superior models will have a flexible architecture, ensuring program compatibility from the bottom up. Their architecture is also oriented to efficient realization of high-level programming languages to sharply reduce labor and machine-time outlays for development and debugging of complex application programs, to a rational combination of junior and superior models of the small computer system (as well as of the unified system computers) in multimachine complexes, and to the development of the principles of building multiprocessor complexes with specified reliability, viability and throughput.

Based on these prerequisites, five new classes of models are planned in the program for the second phase of the system of small computers.

The first class of models of second-phase small computers are the microcomputers built with microprocessor sets (models of the SM-50 class). This class is intended for mass application in systems for numeric program control, for building into complex scientific and measuring instruments, intelligent terminals and terminal stations for office work. Based on the SM-50 class of microcomputers, general-purpose controllers are being developed that will enable raising considerably system throughput by transferring some operating system functions to hardware.

The second class are the system compatible small computers of the SM-51 class that ensure continuity of the software and entire series of peripherals with first-phase models. The technical and economic characteristics of these models (speed of response, size, power consumption, storage capacity, etc.) must be substantially (two- to fourfold) improved compared to first-phase models by shifting to a new element base and more progressive technological design solutions.

The third class are models of the SM-52 class which have greater throughput, memory capacity and structural reconfiguration capabilities in the small computer system. Multiprocessor versions of the models are possible. SM-50 and SM-51 class computers may be used as input-output channels in these models. Being intermediates between small computers and unified system machines in their capabilities, these models are suitable for small problem-oriented networks in hierarchic integrated control systems.

Models in the SM-53 class are actually multiprocessor and multimachine complexes built with modules of the other classes, hardware for intermachine and interprocessor communication and integrated software which ensures a rational distribution of the computing process over the system facilities.

#### FOR OFFICIAL USE ONLY

SM-54 class models are specialized processors that realize individual algorithms (such as fast Fourier transformation, matrix operations, etc.) by hardware and make it possible to obtain with these algorithms a very high throughput, exceeding that of large high-speed computers by an order of one-two. Using these processors in combination with models of other second-phase small computer system classes will make it possible to build efficient systems for data processing in the real-time mode in applications such as analysis and synthesis of speech, analysis of aerial photography, analysis of seismic prospecting results and others in which the application of today's computers is limited because of their low speed of response.

In addition to the new classes of models in the second-phase small computer system, plans call for development of a large number of new peripherals with rather high quality. Especially worth noting is that the second-phase small computer system will have a broad range of various types of terminal stations that, on the one hand, will be capable of autonomous data processing at the work station, and on the other, will provide user access to a higher-ranking computer network when needed.

In addition to the directions associated with development of hardware and computer complexes, a broad program of software development is planned. In the software development, consideration is being given to the specific nature of small machines, which does not permit giving the programmer a large choice of hardware as is done with large machines. On the other hand, the necessity of ensuring operation of the small computers in systems and in the required modes (real-time, burst, data acquisition, interactive, time-sharing) determines the expediency of developing a set of operating systems, each fo which efficiently realizes some one of these modes. Such systems are considerably simpler than the general-purpose systems of large computers.

To facilitate programming of various application tasks, development is underway on programming systems that would require the user to specify only the functions needed, relieving him of concern for how this will be performed. Efforts are also in progress to develop more efficient problem-oriented programming languages and the corresponding translators.

COPYRIGHT: Izdatel'stvo "Statistika", 1980

8545

CSO: 1863/157

#### FOR OFFICIAL USE ONLY

SM-52/10 SMALL COMPUTER

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980 (signed to press 17 Nov 80) pp 10-13

[Article by Ya. Gantner, engineer, Hungarian People's republic. from book "Computer Technology of the Socialist Countries", a collection of articles, edited by M. Ye. Rakovskiy, Izdatel'stvo "Statistika", 16,000 copies, 168 pages]

[Text] The experience gained while successfully developing the first phase of the system of small computers (SM EVM) and the effective use of these computers in various sectors of the national economy have determined the need for developing high-throughput small computers suitable for systems of hierarchic control and automation. Developing high-throughput small computers is a major task of the program for the small computer system.

Modern electronic elements, new technology, more efficient software and the experience of international cooperation on the YeS [unified system] and small system of computers have made it possible to begin developing the SM-52/10 model at the VIDEOTON plant (VNR [Hungarian People's Republic]).

The SM-52/10 has a flexible architecture which makes it possible to easily change the configuration of a system to match the problem to be solved. This computer can use the applications programs developed earlier for the small computer system, and at the same time, for more complicated applications, it has the capabilities offered by flexible architecture and programming.

In designing this model, the "3M principle" was realized: modularity (of hardware and software), microprogramming and a monobus system.

The main principles realized in developing the architecture of this model are: optimal distribution of tasks between hardware and software;

support of a multifunctional mode by hardware and microprograms;

mutual protection of applications and systems programs while maintaining good communication between them;

capability of using software developed earlier; and realization of advanced "self-diagnostics."

#### FOR OFFICIAL USE ONLY

Realization of the design principles makes it possible to simultaneously solve different types of problems on one and the same (logical) computer while providing practically absolute protection of them from each other.\* Division of the functions of the central processor is afforded by the technology of ESL- [emitter-coupled logic = ECL] (which up to now has practically not been used in small computers), TTL [transistor-transistor logic = TTL] and MOP-BIS [metal-oxide-semiconductor = MOS large-scale integrated = LSI circuits]. Floating-point or decimal operations are performed in supplementary units, and, for example, separate functions of file processing are supported by a microprogram memory realized in interface units (in some cases with a capacity up to 10 Kbytes).

The models have no traditional complicated control console; the method of remote loading of programs and the method of remote diagnostics have been developed and realized. The latter method affects the qualitative variation in hardware maintenance. To satisfy requirements primarily for management of small data bases, the model SM-52/10 has a main memory with a capacity up to 1M byte and auxiliary storage on disks with a capacity up to 200 Mbytes. The speed of the processor is maintained by buffer cache\*memory by matching the transmission rate between the memory and other system elements. Terminal control and connection to networks is effected through synchronous and asynchronous lines.

The model SM-52/10 has a multilevel (64) system of interrupts. Instructions have the format of a word (16 bits) and data may have the format of a halfword (byte), a word (16 bits) or a double-word (32 bits) with floating decimal. The microprogram memory is made in the form of RAM [random-access memory] on-line memory. Part of the memory is reserved for user needs, for example for expanding the system of instructions. An integral part of the central processor is the microdiagnostics which test the processor and cache memory and operate with each switch-on, but may also operate upon command from the operator's console.

The central processor consists of the following standard modules: interface, cache memory, arithmetic-logic unit and clock.

Besides the bus for memory and peripherals, the processor has a synchronous bus for rapid internal communication between processor modules and between the processor and special operating units.

The cache memory, in essence, is a "rate interface" between the relatively slow main memory and the fast arithmetic-logic unit built with ECL processor sets. The capacity of the cache memory is 8K words and each element in it is organized in the form of a pair of words: a word with an even address and a word with an odd address. Access to it during any reference to memory is effected by the low order bits of the even address. If the word sought is in the cache memory, then communication with the main memory is not required, as a result of which execution of operations with reference to memory is accelerated considerably (approximately 90 to 95 percent of the operations using memory are executed with the cycle time of the cache memory, i.e., about 250 ns).

11

Up to now, this property had been the exclusive privilege of only large computers.

\*\*

A cache is a fast semiconductor memory.--Editor's note.

The arithmetic-logic unit is made with high-speed microprocessor sets of the bit slice type; it contains the arithmetic module and the control fields for the microprogram memory. Addressing of microinstructions, decoding of the instructions and checking memory segmentation is performed by the control module. The microprogram memory may be loaded, and the microprocessor updates it. The control microprocessor reads the main microprograms from the read-only memory [ROM] to establish the initial states, and other microprograms are read from main memory.

The operational units are used to raise the efficiency of the operations of FORTRAN (with floating point) and COBOL (decimal); the units provide for hardware execution of instructions oriented to high-level languages. The efficiency of various translating programs may be significantly enhanced by incorporating such special units.

The second processor, created from basic modules with microprogram memory, is used for emulation. It is possible to use a large number of such processors to realize other systems of instructions. Thanks to the high level of technology, the time for execution of instructions typical for emulated architectures is no worse than with the source modules.

The microprocessor interface units used for very high throughput peripherals unload the processor to a considerable extent. In essence, they are a processor, transformed into a functional exchange control unit and a unit for direct access to memory. These processors perform organization of data flow and control typical for a peripheral in an autonomous mode. In accordance with the modular principle, exchange processors differ from each other usually only in content of microprogram memory. More "intelligent" interface units provide for execution of many new functions for control of data transmission using interfaces created for various data transmission networks (for example, synchronous and asynchronous interface, X-interface according to ISO [International Organization for Standardization] standards and others).

The model contains integrated and high-throughput units for control of peripherals; in addition, there is the capability of connecting peripherals to a simple standard bus system. Used as peripherals (with regard to standardization) are the peripherals for the YeS and SM computers in accordance with requirements of throughput and economy. For man-machine communication, the most efficient and convenient ATsPU [alphanumeric printers] and displays with microprocessor control are used. Controls and indicators on this equipment have been designed with maximal regard for human engineering requirements.

The decentralized functions embedded in the hardware promote optimal selection of software and ensure balance within the bounds of "cost versus productivity" and "outlays for production versus cost of utilization."

The concept of the SM-52/10 computer and the schedule for implementation allow considering it as one of the first models of the second-phase system of small computers. It may be used extensively to solve the more complicated class of problems that impose special requirements on a computing system.

#### FOR OFFICIAL USE ONLY

The author considers extremely important giving prompt assistance to users to train them to operate this high-throughput computer, since experience shows that use of the capabilities embedded in individual models depends on the degree of user training. The design of this model will make it possible to relieve the user of a number of routine maintenance tasks.

These efforts are being made in close international cooperation with users and scientific institutions with respect to critical evaluation of the operating experience of previous models.

COPYRIGHT: Izdatel'stvo "Statistika", 1980

8545

CSO: 1863/157

MODULAR CONCEPT IN DEVELOPMENTS OF GDR DATA PREPARATION UNITS AND TERMINALS FOR YES AND SM COMPUTERS

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980 (signed to press 17 Nov 80) pp 13-19

[Article by G. Merkel, engineer, GDR, and H. G. Jungnickel, engineer, GDR, from book "Computer Technology of the Socialist Countries", a collection of articles, edited by M. Ye. Rakovskiy, Izdatel'stvo "Statistika", 16,000 copies, 168 pages]

[Text] The decade of cooperation between the socialist countries in computer technology is part of the socialist economic integration. The Robotron Combine's contribution to this integration has been the YeS-1040 and YeS-1055 computers which are operating successfully in various countries, and the 10 devices in the system of small computers (among which are two second-phase microcomputers) developed and put into production (before 1979).

Robotron produces not only central processors for the YeS computers; it is a major producer of serial printers and peripherals, particularly data preparation units, data teleprocessing devices and various special-purpose terminals, displays, magnetic tape cassette storage units and optical readers. Mass production os such small computers as the Cellatron 8205 and the Robotron 4000/4201 have made it possible to acquire experience for participation in developing the SM computers.

In accordance with the specialization in YeS and SM computers, the tasks of the collective are:

to expand production of the YeS-1055 computers. The modernized version of this model will be equipped with a matrix module that will make it possible to solve the expression a + bc with a high speed and thereby increase 10 to 50-fold the speed of execution of this class of problems. The matrix module, made as an individual special processor supplementing the standard processing unit, will allow direct transmission between the matrix module and storage. Efforts continue to further modernize the YeS-1055 computer. For example, it is planned to increase the capacity of the main memory to 8 Mbytes, using semiconductor highly integrated memory circuits;

to participate in developing operating systems and application program packages for the second series of YeS computers. The program package developed in the GDR provides the capability of using Unified System Computers on the virtual machine principle, which will allow achieving high efficiency in developing user programs. The shift to using new efficient operating systems is being facilitated;

#### FOR OFFICIAL USE ONLY

to make full use of the expertise and technical and economic potential in developing small computers, peripherals and storage units for the YeS and SM computers and data preparation devices. In the process, it should be oriented to the areas in which the equipment developed by the combine has been used with success for many years now. These are banks, financial agencies, trade organizations, agricultural enterprises, statistical administrations, railroad administrations and the entire area of economic calculations in industry, construction and other social areas.

Basic Hardware Requirements. The hardware under development to meet user demands is used more and more in various fields of science and technology. In connection with this, new requirements for them are also emerging. Studies and analyses were made of user requirements for hardware in which man is allocated the role of operator-executor. Based on these trends in computer application, an analysis was made of those fields of application in which

a clear shift has been noted from autonomous small-scale data processing to complex data processing (among which are teleprocessing systems with central computers of the YeS and (or) SM systems);

data preparation requires new engineering solutions, primarily in problem-oriented intelligent terminals directly in the workplace; and

use of terminals with broad problem orientation in teleprocessing systems will make it possible to substantially raise the efficiency of control processes (in the field of mass servicing and production, in financial institutions, etc.).

In these fields, the hardware is used under conditions differing from those, for example, in automating an industrial process. To obtain a solution effective for computer users, both general and specific requirements must be considered.

General Requirements Imposed by Users on Hardware.

- 1. Clarity, i.e. the operation of people with a system must look simple, despite the complex processes occurring in the system.

- 2. Capability of system expansion. Usually for the user, the fundamental requirements are:

capability of simple forms of expanding the configuration, for example by peripherals and additional memory (as a rule, this requirement is being met);

capability of system expandions: expansion of the capacity for addressing, the list of instructions, connection of compatible units of devices for proportional increase in the overall throughput of the equipment (for example, connection of large external storage devices without overloading the channels);

capability of using efficient compatible programs, programming languages, data bases or files, and operating systems;

capability of simple adaptation of the system to new user requirements, i.e. flexibility, for example, by replacing microprograms.

3. Unity of principles of solution. This requirement significantly raises system operation efficiency:

common engineering solutions allow the user to reduce the quantity of spare parts and time for training maintenance personnel, and to reduce downtime and repair time;

common logical and functional principles make it possible to better track system operation within a device and between different devices, make it easier for users to develop program packages for various fields of applications, reduce outlays for operation with devices and simplify maintenance of the different system units.

- 4. Adaptation of hardware and software to human habits. The most abundant requirements are dictated by human engineering: location and layout of the keyboard, location of the display and text on a screen, referencing various devices and data media (for example, changing magnetic tape cassettes). Other human engineering criteria are adaptation of shape and color to the environment, and consideration of human habits in organizing machine operation. For example, the custom of letting the operator see immediately the symbol input by him through a keyboard on a screen or printer. Waiting in the course of a second makes him unsure and lowers productivity. However, if the computer response appears immediately on the screen during interactive mode operation while solving complex problems, an operator tends to feel that he is being "urged on" and he tires quickly. A waiting time of 1 to 2 sec. in solving such problems may be considered a fast response. But if an operator has to wait more than 5 sec. in solving simple problems, his work rhythm is disrupted. In this sense, adaptation calls for extensive system analysis.

- 5. High system reliability. For example, terminal reliability must be more than 98 percent for the commercial user. However, high reliability must not be achieved through high economic outlays.

- 6. Small outlays for teaching programming and maintenance of the various system devices.

These requirements are equally legitimate for YeS and SM computer users. Development of standardization and modularity of this equipment has determined the task of developing a common technology for analogous directions of application of YeS and SM computers with regard to reasonable compromises with respect to interfaces, control procedures, etc.

Specific User Requirements. Specific requirements for hardware to be developed are defined by the working process of users. These requirements include various data media adequately equivalent for the user, various logging equipment, use of various programming languages, etc. For example, it is natural for a user used to working with magnetic cards to want attachments for processing these cards on new accounting and office machines, and for the user who has not worked with magnetic cards to want floppy disks. Terminals used in banks and those used to make reservations are almost the same in the interactive procedure. Both terminals are elements of a multiaccess system controlled by a computer and require response time on the order of a second, etc. But there are specific differences: the technique of printing tickets and reserved seat tickets differs completely from issuing bank documents or making entries in savings-bank books.

These legitimate specific requirements limit the selection of hardware for maintaining a dialogue and presenting the results (parameters, entries, data) to the user.

These facts were used in developing the new concept: the modular concept for the units was compiled in accordance with general system requirements. Specifications of the YeS and SM computers were considered as general conditions.

#### FOR OFFICIAL USE ONLY

General system concept of autonomous devices, complexes and subsystems. The basis of the sets of data preparation units, devices for communication with a computer, and microcomputers developed at the Robotron Combine were the features of application discussed, general specifications, and the general and system provisions of the YeS and SM computer systems. Development proceeded according to the following basic rules.

- 1. Problem-oriented complexes and individual devices, as items to be marketed, are developed on the basis of standard units and devices, unified operating systems and software components, as well as problem-oriented special units and problem-oriented software components.

- 2. The set of unified units and individual devices is restricted; they are developed as general-purpose as possible and are subject to strict standardization. Used, for example, are:

the two main trends of unified units of microcomputers of the SM-5040-2 type as the 8-bit version and the SM-5050/5110 as the 16-bit version, compatible with the architecture of the system of small computers;

two types of serial printers, compatible design and system engineering wise, with a rate of 30-400 characters per second;

three main types of video monitor units;

two basic types of keyboards; and

a unified series of power modules and a whole assortment of other peripherals in accordance with the design specifications for the system of small computers, including a considerable number of purchased units from the nomenclature of the YeS and SM computer systems.

- 3. Items are developed within the bounds of a common basic design in various forms of execution based on CEMA standard No 834-77. This common basic construction allows common design realization of seats, console devices and table devices. Production is carried out by common industrial methods. These design solutions realize the basic provisions of the system of small computers, are efficient for auvanced devices of the unified system of computers and meet the requirements for application of modern microelectronics.

- 4. The individual devices and complexes for application, used as a remote terminal or subscriber's station within data teleprocessing systems, presuppose efficient adaptation to the various control procedures and transmission algorithms which have already been adopted or must be adopted in the YeS and SM computer systems. In addition, facilities are offered for efficient adaptation to specified operating systems.

- 5. For rational development of problem-oriented programs outside the bounds of the proposed extensive standard assortment, efficient technology exists, including appropriate aids for programming and complexes for developments, which may be offerred also to major users and thereby will make it possible to reduce the continuously increasing outlays for programming.

- 6. The set of unified assemblies and units, software components and special components is an open system, i.e. it is continuously supplemented within the bounds of the specified principles.

A series of devices and problem-oriented complexes within the YeS and SM computer systems has been and is being developed on this basis. The first of these devices and some basic modules were shown at Moscow at the Second Joint Exhibit of the Computer Technology of the Socialist Countries (1979):

the Robotron MFG 20—a general-purpose programmable terminal made in the form of an individual work station;

the Robotron DEG 20--a programmable device for data preparation with properties of a terminal (desk-top device);

the Robotron PRT 20--a programmable complex device for reservations, also with properties of a terminal;

the Robotron MRES 20-a system for development of programs for all items based on the  $8-bit\ SM-5040-2$ ;

the SM-5040-2 microcomputer;

the Robotron 1152 serial printer; and

the Robotron K 5251--a device with cassette magnetic tape conforming to the ISO standard TC 97/2-35.

System diversity of devices may be achieved based on the unified core of a control computer and strict unification of other main components. This approach made it possible to focus efforts in software development on the more important problems and to combine the principle of modularity with high throughput of operating systems.

The Robotron Scientific Production Combine is also working on 16-bit microcomputers with varying capacity, and these are used as the basis for developing efficient problem-oriented complexes and devices to control data teleprocessing. These complexes and control devices are, for example:

complete minicomputers for scientific, technical and economic problems in all spheres of the economy. GDR efforts in minicomputers enter fully into the program for development of the system of small computers. These machines may be used both autonomously and in direct communication with a computer as a terminal or subscriber station for a YeS computer. Their configuration has a large set of peripherals of the system of small computers, multiplexors and general-purpose terminals. Offered as operating systems are primarily the SM computer operating systems for computing centers oriented to disk storage, the SM computer operating system for application in real time and software for the base computer, especially for a YeS computer;

general-purpose systems for data preparation for autonomous preparation of mass information at enterprises, combines, research institutes and other institutions or for direct communication with computers. Here too the system control unit of the SM computer serves as a central core, to which along with the most varied peripherals are also connected multiplexors and terminals (primarily problem-oriented). In addition to general-purpose operating systems, special software components are needed. Subscriber stations of the YeS-8505 or YeS-8506 type will be developed further by connecting other special devices for preparation of production data and production control;

#### FOR OFFICIAL USE ONLY

a series of multiplexors and concentrators. Modular structure will allow realization by common concept of several versions of data teleprocessing control units with regard to the latest requirements. These devices are intended for use in YeS computer networks and may as a multiplexor have a YeS computer channel adapter or process YeS computer control procedures as a concentrator; they may also be used for similar functions in the system of small computers. In addition to data transmission control through various interfaces, these devices are used to monitor control and teleprocessing of information, and to realize such problems of data teleprocessing as code conversion, buffer storage of messages, message processing, adaptation of procedures, addressing of channels, message distribution, etc.

COPYRIGHT: Izdatel'stvo "Statistika", 1980

8545

CSO: 1863/157

#### DEVELOPMENT OF SMALL COMPUTERS IN CUBA

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980 (signed to press 17 Nov 80) pp 19-23

[Article by L. H. Karrasko, engineer, Republic of Cuba, from book "Computer Technology of the Socialist Countries", a collection of articles, edited by M. Ye. Rakovskiy, Izdatel'stvo "Statistika", 16,000 copies, 168 pages]

[Text] The development of small computers, begun in the Republic of Cuba in 1969, for automated systems for real-time control and monitoring of the sugar harvest is being continuously improved. Subsequently, the program of research and concrete developments received an additional orientation to new objects where these systems could be applied with great effectiveness. In particular, the research program was aimed primarily at implementing a system for planning and management of the national economy, as well as technical, scientific, social activity and others. A major task was developing hardware for export.

The small computer development program in the republic includes not only designs, plans and specifications for the short term, but is also part of a long-term program for computer hardware development in the Republic of Cuba to 1990. A major characteristic of the effort on development of computer hardware (SVT) is that it is determined by the problems, methods and forms of international cooperation that are specifically expressed in the Agreement on Multilateral International Specialization in Developing and Producing Computer Hardware, adopted by the MPK po VT [Intergovmental Commission on Cooperation between the Socialist Countries in Computers].

Specialization by the Republic of Cuba has special importance for successful development of computer technology in the country, since it will allow applying high throughput machines and progressive technology, building enterprises with optimal scales of production ensuring their high profitability, and conducting an effective export policy. On this basis, cooperation between the Republic of Cuba and the countries participating in the MPK po VT is being improved and expanded.

The participation of Cuban specialists in the work of the MPK po VT has made it possible to exchange information on the status and evolution of this complex technology, to cooperate in scientific research and design, to forecast and implement scientific and technical analysis and exchange technical documentation. Cuba's participation in the agreement on specialization and cooperation in computer production guarantees the country high economic effectiveness in the production, export and import of this equipment and at the same time allows achieving a high technical level and quality in production.

The SID-201 Series of Small Computers. The first group of models of SID-201 small computers were developed over the period from 1969 through 1977. It includes four type models: the SID-201, SID-201A, SID-201B (basic) and the SID-201B (expanded). These models were not compatible with the unified models developed in the other socialist countries. The SID-201 series of small computers is not a family; it is a development of a set in which the technical structure or architecture has one common line (set of instructions, memory word size, system of addressing and others). The early models of this group were the components for the later ones.

The first system, designed and built in 1969-1970, was the model SID-201. It confirmed the capability of producing it in Cuba, despite the great difficulties in providing for the technology of production. The system SID-201 was used in sugar plants, particularly for organization and monitoring of rail transportation for the sugar industry. It was noted that with generalization of some characteristics and connection of a minimal number of peripherals, this system could be used not only in the sugar plants, but in any other sector of the national economy. To this end, the system SID-201A with expanded software capabilities was developed.

The model SID-201A was the first computer put into series production in 1970-1972. The series was comprised of 20 units; in the process, more modern technology of production was achieved, and system reliability and economy was raised. System throughput is 25,000 to 50,000 operations per second; the main memory with a capacity of 4K words with 12 bits each is organized into pages of 128 words each; there are four forms of addressing memory. This system furnished classroom and on-the-job training for specialists in this technology.

The model SID-201B (basic) was developed in 1972 and its production was begun in 1973. This model had greater capabilities than the SID-201A; the experience gained in designing and producing the previous models was taken into consideration in the development. The main memory was organized on a modular basis which made it possible to increase the capacity from 4 to 32K words. The instruction set was expanded 1.5-fold, and a system of interrupts from peripherals was provided. Software was improved and the number of programs increased. According to assessments by Cuban specialists, there was about a 10-fold increase in power and operating capabilities with the SID-201B (basic) system compared to the SID-201A.

This model underwent further development in an expanded configuration, where the central processor in general features was the same as that in the SID-201B (basic); interface units and a direct-access channel were added, which significantly increased the system's technical capabilities, having provided the capability of connecting a large number of peripherals. Development began in 1975 in connection with the need of introducing a new system for managing and planning the economy in the country. The system has fundamentally new characteristics compared to previous one: input of standard perforated cards at a rate of 320 cards per minute and an interface of peripherals through slow and high-speed channels make it possible to transmit data at a high rate without delay.

The model SM-2302 small computer (SID-300) is one of the first results of the unified direction of developments and production of computer equipment by the countries participating in the agreement adopted in 1975. Development of this computer began in 1976. Three pilot models were developed which successfully passed joint international tests in the USSR in 1978. This computer was included in the

family of the system of small computers with the designation of SM-2303. The SM-2303 is now being put into series production.

In its element base, architecture and software, the SM-2303 is among the advanced models produced in the socialist countries. The element base (developments of the socialist countries) has a medium and high degree of integration. Thanks to the standard interface, a number of different peripherals may be connected to it, beginning with electromechanical and ending with magnetic with large capacity. The instruction system is more powerful than in the small computers of previous models. Twelve forms of addressing allow increasing the efficient rate of computation and facilitate using the computer. The system of interrupts has four levels of priority which considerably increases the power of the machine and also facilitates operating it.

The model SM-50/40-1 microcomputer (SID-400) was developed completely on the basis of large-scale integrated circuits (BIS) and microprocessor sets developed in the socialist countries. This model has perforated tape input and output and additional storage on floppy disks. The system is useful wherever automation of engineering and adminsitrative activity is being delayed because of the high cost of small computers, and also because of the requirements for their operating conditions; this is primarily the small enterprise or specialized department of economic activity. Up to now in Cuba, this problem had been solved partially through import of calculating machines, which besides their high cost had other shortcomings too, such as relatively low productivity, limited application, much space occupied, etc. Development of a family of SM-50/40-1 machines will make it possible to avoid these shortcomings.

The microcomputers will also be used as elements of the SM-2303 system of small computers (modular construction) and in computer networks.

The SM-7203 Video Terminals (SID-702). Development of peripherals has been proceeding along with development of the small computer system. The first result is the SM-7203 (SID-702) alphanumeric video terminal. Three pilot models were developed which successfully passed joint international tests in 1978.

The SM-7203 has a set of 64 different ASCII [American Standard Code for Information Interchange] characters; 20 lines of 72 characters per line may be displayed on the screen. There is also a standard alphanumeric keyboard. The terminal operates in two modes: standard and with a computer. Among the capabilities this unit offers users are:

blinking or normal cursor indicating position of next character;

insertion or deletion of characters or line of text;

cursor movement in any direction, position by position or continuous;

adjustable margins for text being transmitted; and

scrolling.

The terminal has an audio signal to indicate line or screen margin.

#### FOR OFFICIAL USE ONLY

Future developments. Under development now is a more powerful computer (the SID-300/20), compatible with the SM-2303 as well as with other models of the system of small computers. This new model will have a higher degree of integration and a larger main memory.

In the development of microcomputers, research and development is underway on new, more powerful machines (the SID-400/20); and solutions are being sought to expand their application in the national economy.

Development is also proceeding on several models of video terminals, based on components of larger-scale integration, including a microprocessor.

Unity in the engineering policy for development ensures assimilation of new models without special additional efforts (particularly in training specialists to operate them), as well as the capability of development of application and the compatibility of systems.

COPYRIGHT: Izdatel'stvo "Statistika", 1980

8545

CSO: 1863/157

#### PRINCIPLES OF BUILDING MULTILEVEL AUTOMATED CONTROL SYSTEMS

Moscow VYCHISLITEL'NAYA TEKHNIKA SOTSIALISTICHESKIKH STRAN in Russian No 8, 1980 (signed to press 17 Nov 80) pp 23-29

[Article by R. S. Sedegov, doctor of economic science (USSR), V. A. Bashko, candidate of economic science (USSR) and A. M. Shipulin, engineer (USSR), from book "Computer Technology of the Socialist Countries", a collection of articles, edited by M. Ye. Rakovskiy, Izdatel'stvo "Statistika", 16,000 copies, 168 pages]

[Text] The shift to development of complex systems with automation of control at all of its levels has become a real necessity and characterizes the new stage in the development of ASU [automated control systems = ACS]--multilevel automated control systems.

The lack of a unified concept for building systems to control production (associations, combines, enterprises) causes the emergence of various, often contradictory, requirements for the organization and technology of developing and implementing the systems, and makes it impossible to establish general norms, rules and standards, and prescribed procedures for the development, implementation and functioning of the systems. Therefore, it is becoming especially urgent to develop a systems methodology for building multilevel ASU's that ensure coordinated control of the various production and industrial objects, integration of control procedures and methods, and integration of the processes for design of the controlled objects and control systems, as well as their assimilation and functioning.

A multilevel automated control system is a complex man-machine system based on a computer and teleprocessing hardware, intended to obtain needed data and to control an association and its structural units. It realizes control of an association, the enterprises and industrial processes, coordinated in goals, criteria and procedures for data processing. A multilevel ACS includes these levels: the upper level—an ACS for a production association (ASUPO), the middle level—an ACS for an enterprise, branch, shop or section (ASUP), and the bottom level—an ACS for industrial processes (ASU TP).

A multilevel ACS must ensure output of a product with the least physical, manpower and cost inputs. The use, parallel with traditional control methods, of uncoordinated systems for control of individual industrial and organizational processes does not, in the majority of cases, yield the necessary efficiency of control. The determining role in the development of a multilevel ACS is played by the mutual coordination of the purposes of control at all levels and the well-grounded selection of

## FOR OFFICIAL USE ONLY

the criteria of efficiency in strict accordance with the established purposes of control, participation of administrative personnel in development of the systems, and organizational, hardware, software and data compatibility. In a multilevel structure of an integrated system for control of an association and an enterprise, each control unit must perform the tasks of the senior unit and in turn establish the target tasks, limitations and criteria for the control units subordinate to it.

A multi-evel ACS is a complex control system with a trilevel structure that realizes the following directions of integration:

functional-purposeful (unity of purpose and a system of coordinated criteria); organizational (rational combination of administrative activity of personnel and the ACS);

software (combined and interrelated complex of models, algorithms and programs); informational (unity of sources and files of data); and

hardware (unification of the hardware complex to raise the throughput and reliability of the computer data network).

A multilevel ACS must perform the selected functions of control of specified objects on the basis of

coordination of goals and the problems that are to handled by the system and its individual subsystems (components);

formulation of a rational structure of the control system;

interlevel exchange of information;

coordinated solution of control problems of the different levels; and

organization of interrelation between automated systems for planning, accounting and monitoring and systems of industrial automation.

Development of a multilevel ACS is a complex problem, for the realization of which the countries of the socialist community have been enlisted within the framework of the Council on Application of Computer Technology. In developing a multilevel ACS, the following principles must be realized:

systems approach under the conditions of limitations on resources;

compatibility of all types of support (organizational, informational, hardware and software);

rational combination of centralized and peripheral hardware for data processing;

integration of levels by purposes, criteria and procedures of data processing;

maximal utilization of NIR [research] conducted by the socialist countries in accordance with the plans of the Intergovernmental Commission on Computer Technology; and

the capability of ACS functional evolution as experience is gained and new structures and industrial objects are connected.

The hardware complex (KTS) of a multilevel integrated ACS (IASU) is a complex system, consisting of interacting hardware complexes of the ACS's of all three levels, including facilities for acquisition, storage, processing, presentation and transmission of information, as well as the hardware to interface them, which result in solving the complex of problems of all classes of the multilevel ACS.

The intricate system of the hardware complex stems from the need of using various structures of hardware and methods of realizing the goals set (the problems). The hardware complex of multilevel ACS's must meet the following requirements:

capability of building hierarchic and multiprocessor computer complexes;

use of data transmission networks and teleprocessing facilities;

use of small computers for preparation and decentralized processing of data, and for control of industrial processes and equipment;

capability of acquiring valid data under the conditions of production interferences and personnel errors;

reliable operation of individual hardware complexes in an aggressive environment; hardware, data and software compatibility;

validity of problem solving;

minimal outlays for hardware maintenance; and

short payoff period and high economic effect from introduction of the multilevel ACS.

As base equipment for the system's top level, third-generation medium and large computers—YeS and SM EVM [unified system and system of small computers]—must be used. The SM-1, SM-2 and SM-3 series of small computers must be used extensively at the bottom level of a multilevel ACS as machine-dispatchers, for preliminary data processing and for controlling industrial processes.

As network terminal equipment at the bottom level of an integrated ACS, subscriber stations and terminals that support data input and storage and output of results must be used. Two types of terminals are used: simple with hardware control and input-output equipment, and terminals with input-output equipment and a small computer for program control and preliminary data processing. Terminals operating in real time may obtain data from sensors, metering instruments, etc. The terminals developed may accept and put data into a computer and edit data. The most widely used terminals for a data teleprocessing system within the unified system are the subscriber stations. A subscriber station is one or several unified system peripherals with a special control device performing various functions.

A subscriber station collects, prepares and accumulates data for transmission to a computer, and inputs-outputs and displays data.

Software (PO) for a multilevel ACS must meet the following requirements:

use of a multiprogram real-time operating system for organization of data acquisition and processing;

availability of data bases for use on-line;

reliability of functioning;

restoration of status of data at a specific moment of time; and

maintenance of communications with the software at the different levels, both functional and informational.

#### FOR OFFICIAL USE ONLY

These requirements, as well as a large number of problems in the multilevel ACS's, and the increase in communication and dependence between software components shape the development of the software in two directions: general systems and problem.

In addition to type procedures (input, sorting, etc.), the functions of general systems software include:

organization of system operation in the specified modes;

distribution of computing operations in accordance with their dynamic priorities; monitoring the execution of computing operations;

timely preparation and input of data bases needed;

differentiated access to information in a data base;

monitoring the operation of terminals and small computers;

initiation of operation and control of a teleprocessing system; and communication with the system operator and terminal operators.

Problem software functions are:

loading and management of the information base of normative-reference information; loading and management of real-time informational bases for all levels of the ACS; solving the problems of control automation; and capability of restoring the status of the data.

These software requirements and functions determine the selection of the main components of the general systems software, namely: the operating system, the data base management system (SUBD) and the teleprocessing system.

In selecting an operating system, it is very important to take into consideration the capability of using application program packages developed earlier. Simultaneous operation of different operating systems in an integrated ACS is not ruled out. In selecting a teleprocessing system, the tasks of the multilevel ACS, the requirements for data processing from the user aspect and hardware capabilities must be considered. The determining factors in selecting a teleprocessing system are the type of base operating system selected and the data base management system.

The information base of multilevel ACS's is the aggregate of the unified system of classification and coding of technical and economic information and the unified systems of documentation and files of information used in all levels of the hierarchy. The components of the information base for multilevel ACS's are the data bases for the automated production association control system, the automated enterprise control system, the automated system for control of industrial processes and the data base management system.

Information compatibility of the functional systems means developing coordinated sets of classifiers and codifiers that ensure smooth exchange of information in the links of man-machine and machine-machine at all three levels (production association, enterprise, work place or industrial process).

#### FOR OFFICIAL USE ONLY

One-time input of information for repeated use of it and centralized data processing must be provided for in the system. A centralized data base (TsBD) must be developed for collective use at all levels. Centralization of the information base within the framework of the centralized data base will make it possible to a considerable extent

to tie the ACS's of the different levels and the individual users together with respect to information;

to reduce duplication of data during storage of it;

to increase the identity of information thanks to one-time input and centralized management of it; and

to separate the processes of creating and managing the centralized data base from problem programs.

A centralized data base for a multilevel ACS must meet the following requirements: concentration of information used at the different levels of the ACS and transmitted between them;

capability of partitioning for the different levels of the ACS as a function of priorities and user access restrictions;

simplicity and convenience of creating and managing;

validity of data without discrepancies;

efficient use of machine resources; and

capability of changing the composition and structure as the system evolves.

Also charged with information support of the ACS, besides the centralized data base, are the local data bases oriented to groups of users and even the individual users. Thus, the information base for a multilevel ACS is the aggregate of the centralized and the distributed data bases.

Under these conditions, it is important to properly select the criteria for building the information base and the methods for realizing it.

Problems of organization of development. Full preparation has to be made first of all in sectors of industry where multilevel ACS's are planned. It should be considered that multilevel ACS's will be created under conditions of change in structure and organization of industrial control and introduction of new general schemes for development and siting of production.

In preparing to develop a multilevel ACS in enterprises, there has to be modernization of the industrial equipment largely influencing the parameters of the entire production process.

This preparation, carried out with the use of modern facilities for control of equipment, will make it possible to create the conditions, with the lead time needed, for the overall technical and economic substantiation (TEO) for evolving the list of multilevel ACS's being developed.

#### FOR OFFICIAL USE ONLY

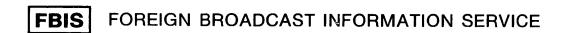

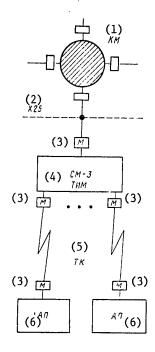

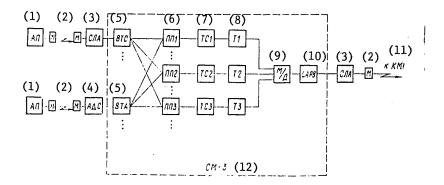

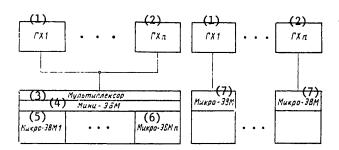

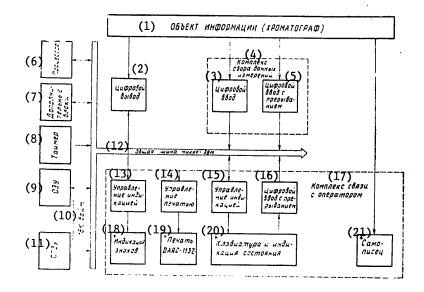

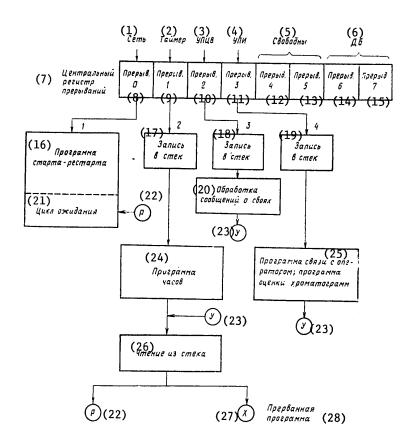

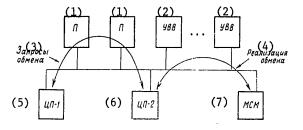

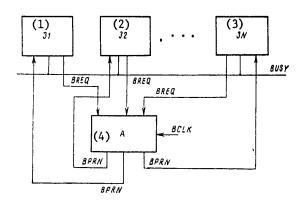

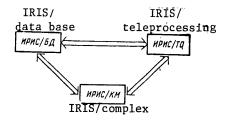

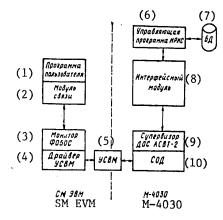

Solving the problem of developing a unfied system of hardware to operate multilevel ACS's is of major importance. The solution must be based on integration of the programs to develop the various means of automation.